ICL7104

Functional Block Diagram

R

C

INT

INT

+15V -15V

BITS

-BUF IN BUF OUT -INT IN INT OUT

OR POL 16 15 14 13 12 11 10 9

8 7 6 5 4 3 2 1

REF

OUT

8

7

1

10

BUFFER

9

11

INTEG.

14

COMP.

5

4

6

7

8 9 10 11 12 13 14 15 16 17 18 19 20 21

6

3

INT.

REF.

COMP

OUT

THREE-STATE OUTPUTS

LATCHES

-

-

A1

+

A2

-

300pF

24

+5V

HBEN

23 MBEN

22

+

A3

5kΩ

8052/8068

+INT IN 12

2

+

-1.2V

5

+BUF IN 13

50kΩ

10kΩ

-15V

LBEN

10µF

C

AZ

COUNTER

30 CE/LD

+BUF IN

33

AZ

COMP IN 300kΩ

36

39

SW3

7104

29 SEN

27 MODE

28 R/H

37

ZERO

CROSSING

DETECTOR

V

SW5

SW6

SW4

REF

CONTROL LOGIC

SW1

SW8 SW2

32

35

ANALOG

INPUT

SW7

SW9

ANALOG

GND

38

REF CAP (1)

34

REF CAP (2)

1

31

2

40

25

26

3

+15V

+5V

-15V CLOCK CLOCK STTS

(1) (2)

C

REF

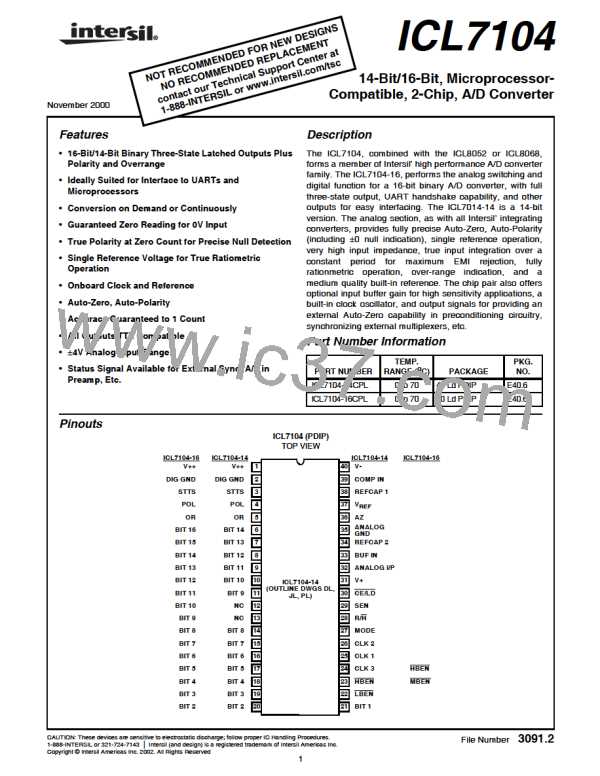

FIGURE 1. ICL8052A (8068A)/ICL7104 16-BIT/14-BIT A/D CONVERTER FUNCTIONAL DIAGRAM

Pin Descriptions

PIN NO.

SYMBOL

V++

OPTION

DESCRIPTION

Positive Supply Voltage: Nominally +15V.

Digital Ground: 0V, ground return.

1

2

3

GND

STTS

Status Output: HI during integrate and deintegrate until data is latched. LO when analog section

is in auto-zero configuration.

4

5

6

POL

OR

Polarity: Three-state output. HI for positive input.

Over Range: Three-state output.

BIT 16

BIT 14

-16

-14

Most Significant Bit (MSB).

7

8

BIT 15

BIT 13

-16

-14

DATA Bits: Three-state outputs. See Table 3 for format of ENABLES and bytes. HIGH = true.

BIT 14

BIT 12

-16

-14

9

BIT 13

BIT 11

-16

-14

10

11

12

13

BIT 12

BIT 10

-16

-14

BIT 11

BIT 9

-16

-14

BIT 10

NC

-16

-14

BIT 9

NC

-16

-14

14

15

16

17

18

19

20

BIT 8

BIT 7

BIT 6

BIT 5

BIT 4

BIT 3

BIT 2

2

ETC [ ETC ]

ETC [ ETC ]