TEA1716T

NXP Semiconductors

Resonant power supply control IC with PFC

I

ocr

I

Cur(HBC)

−I

0

t

t

ocr

I

ss(hf)(SSHBC)

I

ss(If)(SSHBC)

ss(If)(SSHBC)

I

SSHBC/EN

−I

−I

ss(hf)(SSHBC)

V

fmin(SSHBC)

V

SSHBC/EN

V

ss(hf-lf)(SSHBC)

V

fmax(SSHBC)

0

t

V

reg

V

Output

t

Slow soft-start sweep (charge and discharge)

014aaa866

0

Fast soft-start sweep (charge and discharge)

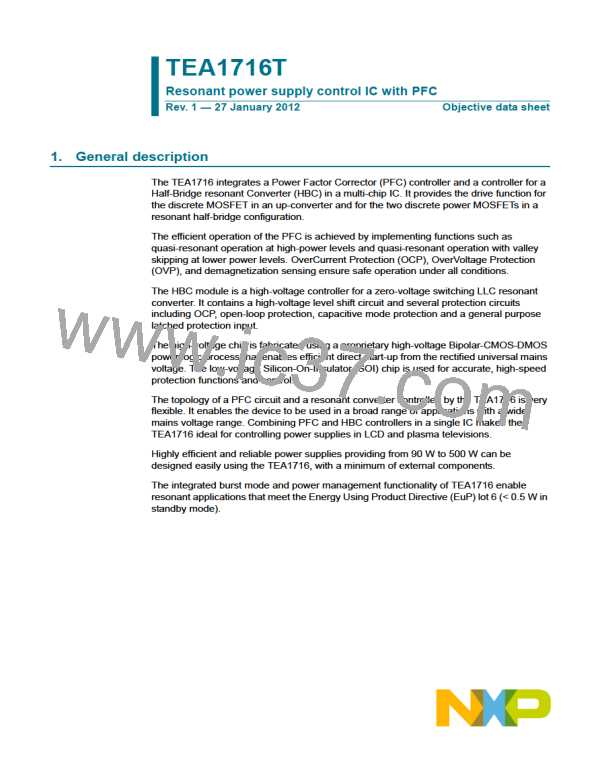

Fig 16. Overcurrent regulation during start-up

The protection timer is also started. The Restart state is activated when the OCR-HBC

condition is still present after the protection time has elapsed.

7.8.10.3 Overcurrent protection, OCP-HBC

Under normal operating conditions, OCR is able to ensure the current remains below the

specified maximum values. If certain error conditions occur, however, it is probably not

fast enough to limit the current. OCP is implemented to protect against those error

conditions. The OCP level, Vocp(HBC) (1.75 V and +1.75 V typical), is higher than the

OCR level Vocr(HBC)

.

When the OCP level is reached, the frequency immediately jumps to the maximum value

via the soft start reset, followed by a normal sweep down.

7.8.11 HBC capacitive mode regulation, CMR (pin HB)

The MOSFETs in the half-bridge drive the resonant circuit. Depending on the output load,

the output voltage, and the switching frequency this resonant circuit can have an inductive

impedance or a capacitive impedance. Inductive impedance is preferred because it

facilitates efficient zero-voltage switching.

The adaptive non-overlap time function (see Section 7.8.4.2) prevents harmful switching

in Capacitive mode. An extra action is performed which results in Capacitive Mode

Regulation (CMR). CMR causes the half-bridge circuit to return to Inductive mode from

Capacitive mode.

TEA1716T

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2012. All rights reserved.

Objective data sheet

Rev. 1 — 27 January 2012

30 of 46

ETC [ ETC ]

ETC [ ETC ]