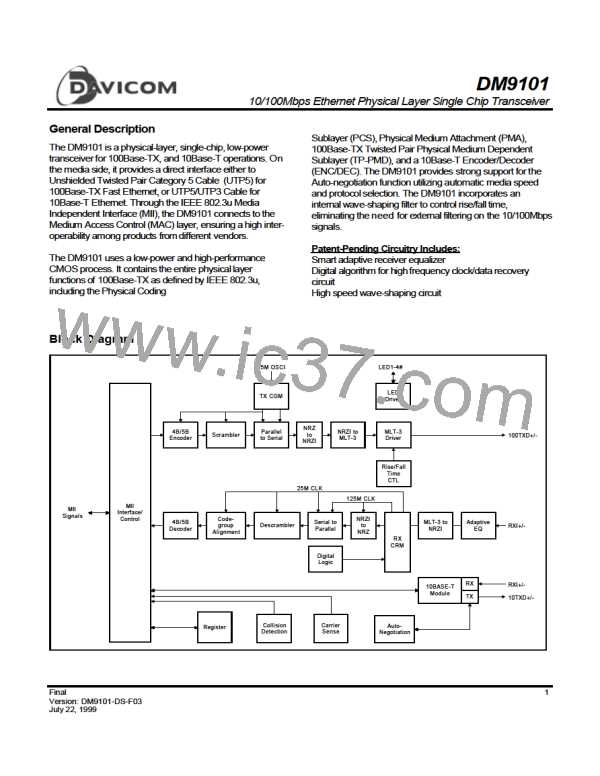

DM9101

10/100Mbps Ethernet Physical Layer Single Chip Transceiver

PHY Identifier Register #2 (PHYIDR2) - Register 3

Bit

3.15-3.10

Bit Name

OUI_LSB

Default

<101110>,RO/P

Description

OUI Least Significant Bits:

Bits 19 - 24 of the OUI (00606E) are mapped to bits 15 - 10 of

this register respectively

Vendor Model Number:

Six bits of the vendor model number mapped to bits 9 - 4 (most

significant bit to bit 9)

3.9-3.4

3.3-3.0

VNDR_MDL

MDL_REV

<000000>,RO/P

<0010>,RO/P

Model Revision Number:

Four bits of the vendor model revision number mapped to bits 3

- 0 (most significant bit to bit 3)

Auto-negotiation Advertisement Register (ANAR) - Register 4

This register contains the advertised abilities of the DM9101 device as they will be transmitted to link partners during Auto-

negotiation.

Bit

Bit Name

Default

Description

Next Page Indication:

0=No next page available

1=Next page available

4.15

NP

0,RO/P

The DM9101 does not support the next page function. This bit

is permanently set to 0

Acknowledge:

4.14

ACK

0,RO

1=Link partner ability data reception acknowledged

0=Not acknowledged

The DM9101's Auto-negotiation state machine will

automatically control this bit in the outgoing FLP bursts and set

it at the appropriate time during the Auto-negotiation process.

Software should not attempt to write to this bit.

Remote Fault:

4.13

RF

0, RW

1=Local Device senses a fault condition

0=No fault detected

Reserved:

Write as 0, ignore on read

Flow Control Support:

4.12-4.11

4.10

Reserved

FCS

X, RW

0, RW

1=Controller chip supports flow control ability

0=Controller chip doesn’t support flow control ability

100Base-T4 Support:

4.9

T4

0, RO/P

1=100Base-T4 supported by the local device

0=100Base-T4 not supported

The DM9101 does not support 100Base-T4 so this bit is

permanently set to 0

100Base-TX Full Duplex Support:

1=100Base-TX Full Duplex supported by the local device

0=100Base-TX Full Duplex not supported

100Base-TX Support:

4.8

4.7

TX_FDX

TX_HDX

1, RW

1, RW

1=100Base-TX supported by the local device

0=100Base-TX not supported

24

Final

Version: DM9101-DS-F03

July 22, 1999

ETC [ ETC ]

ETC [ ETC ]