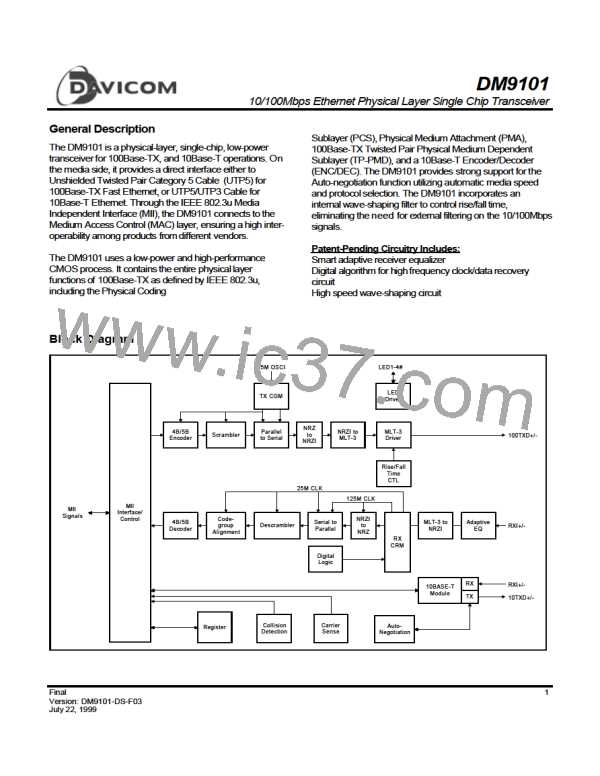

DM9101

10/100Mbps Ethernet Physical Layer Single Chip Transceiver

Basic Mode Control Register (BMCR) - Register 0

Bit

Bit Name

Default

Description

Reset:

0.15

Reset

0, RW/SC

1=Software reset

0=Normal operation

When set this bit configures the PHY status and control

registers to their default states. This bit will return a value of

one until the reset process is complete

Loopback:

0.14

Loopback

0, RW

Loopback control register

1=Loopback enabled

0=Normal operation

When in 100M operation is selected, setting this bit will cause

the descrambler to lose synchronization. A 720ms "dead time"

will occur before any valid data appears at the MII receive

outputs

Speed Select:

1=100Mbps

0=10Mbps

0.13

0.12

Speed Selection

1, RW

Link speed may be selected either by this bit or by Auto-

negotiation if bit 12 of this register is set. When Auto-

negotiation is enabled, this bit will return Auto-negotiation link

speed.

Auto-negotiation Enable:

1= Auto-negotiation enabled:

Auto-negotiation

Enable

1, RW

0, RW

0= Auto-negotiation disabled:

When auto-negotiation is enabled bits 8 and 13 will contain the

Auto-negotiation results. When Auto-negotiation is disabled bits

8 and 13 will determine the duplex mode and link speed

Power Down:

1=Power Down

0=Normal Operation

Setting this bit will power down the DM9101 with the exception

of the crystal oscillator circuit

Isolate:

1= Isolate

0= Normal Operation

0.11

0.10

Power Down

Isolate

(PHYAD=

00000),

RW

When this bit is set the data path will be isolated from the

MII interface. TX_CLK, RX_CLK, RX_DV, RX_ER,

RXD[3:0], COL and CRS will be placed in a high impedance

state. The management interface is not effected by this bit.

When the PHY Address is set to 00000 the isolate bit will be

set upon power-up/reset

Final

21

Version: DM9101-DS-F03

July 22, 1999

ETC [ ETC ]

ETC [ ETC ]