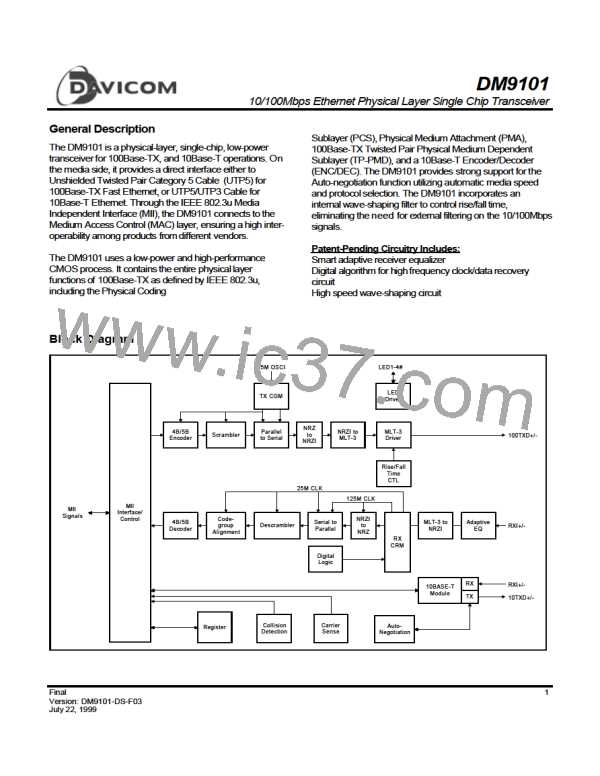

DM9101

10/100Mbps Ethernet Physical Layer Single Chip Transceiver

Basic Mode Status Register (BMSR) - Register 1 (continued)

Bit

Bit Name

Default

Description

MII Frame Preamble Suppression:

1.6

MF Preamble

Suppression

0,RO

1=PHY will accept management frames with preamble suppressed

0=PHY will not accept management frames with preamble suppressed

Auto-negotiation Complete:

1=Auto-negotiation process completed

0=Auto-negotiation process not completed

Remote Fault:

1.5

1.4

Auto-negotiation

Complete

0,RO

Remote Fault

0,

RO/LH

1= Remote fault condition detected (cleared on read or by a chip reset).

Fault criteria and detection method is DM9101 implementation specific.

This bit will set after the RF bit in the ANLPAR (bit 13, register address

05) is set

0= No remote fault condition detected

Auto Configuration Ability:

1.3

1.2

Auto-negotiation

Ability

1,RO/P

1=DM9101 able to perform Auto-negotiation

0=DM9101 not able to perform Auto-negotiation

Link Status:

Link Status

0,RO/LL

1=Valid link established (for either 10Mbps or 100Mbps operation)

0=Link not established

The link status bit is implemented with a latching function, so that the

occurrence of a link failure condition causes the Link Status bit to be

cleared and remain cleared until it is read viathe management interface

Jabber Detect:

1=Jabber condition detected

0=No jabber condition detected

This bit is implemented with a latching function. Once Jabber conditions

are detected this bitwill remain set until a read operation is completed

through a management interface or a DM9101 reset. This bit works only

in 10Mbps mode

Extended Capability:

1=Extended register capable

1.1

1.0

Jabber Detect

0,

RO/LH

Extended

Capability

1,RO/P

0=Basic register capable only

PHY ID Identifier Register #1 (PHYIDR1) - Register 2

The PHY Identifier Registers #1 and #2 work together in a single identifier of the DM9101. The Identifier consists of a

concatenation of the Organizationally Unique Identifier (OUI), a vendor's model number, and a model revision number.

DAVICOM Semiconductor's IEEE assigned OUI is 00606E.

Bit

2.15-2.0

Bit Name

OUI_MSB

Default

<0181H>

Description

OUI Most Significant Bits:

This register stores bits 3 - 18 of the OUI (00606E) to bits 15 -

0 of this register respectively. The most significant two bits of

the OUI are ignored (the IEEE standard refers to these as bit 1

and 2)

Final

23

Version: DM9101-DS-F03

July 22, 1999

ETC [ ETC ]

ETC [ ETC ]