Data Sheet

June 1999

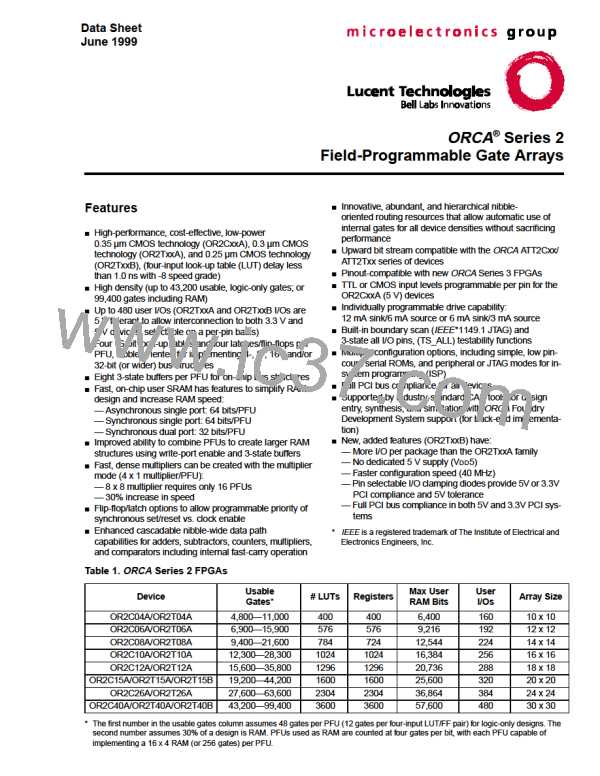

ORCA Series 2 FPGAs

Timing Characteristics (continued)

Table 49. Series 2 Master Parallel Configuration Mode Timing Characteristics

OR2CxxA Commercial: VDD = 5.0 V ± 5%, 0 °C ≤ TA ≤ 70 °C; OR2CxxA Industrial: VDD = 5.0 V ± 10%, –40 °C ≤ TA ≤ +85 °C.

OR2TxxA/B Commercial: VDD = 3.0 V to 3.6 V, 0 °C ≤ TA ≤ 70 °C; OR2TxxA/B Industrial: VDD = 3.0 V to 3.6 V,

–40 °C ≤ TA ≤ +85 °C.

Parameter

RCLK to Address Valid

D[7:0] Setup Time to RCLK High

D[7:0] Hold Time to RCLK High

RCLK Low Time (M3 = 0)

RCLK High Time (M3 = 0)

RCLK Low Time (M3 = 1)

RCLK High Time (M3 = 1)

CCLK to DOUT

Symbol

TAV

Min

0

Max

200

—

Unit

ns

ns

ns

ns

ns

ns

ns

ns

TS

60

TH

0

—

TCL

TCH

TCL

TCH

TD

462

66

1855

265

14840

2120

30

3696

528

—

Notes:

The RCLK period consists of seven CCLKs for RCLK low and one CCLK for RCLK high.

Serial data is transmitted out on DOUT 1.5 CCLK cycles after the byte is input D[7:0]

A[17:0]

TAV

TCH

TCL

RCLK

TS

BYTE N

TH

D[7:0]

CCLK

BYTE N + 1

DOUT

D0

D1

D2

D3

D4

D5

D6 D7

TD

f.44(F)

Figure 67. Master Parallel Configuration Mode Timing Diagram

162

Lucent Technologies Inc.

ETC [ ETC ]

ETC [ ETC ]