Data Sheet

June 1999

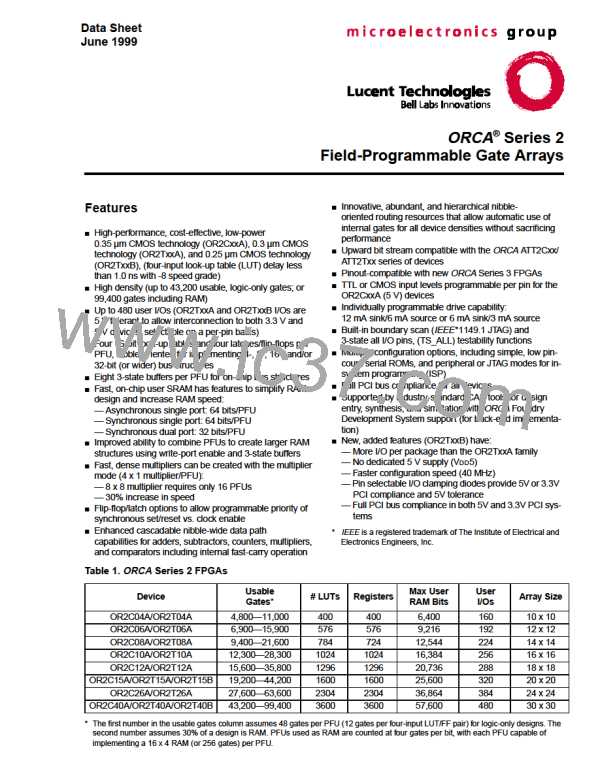

ORCA Series 2 FPGAs

Timing Characteristics (continued)

Table 37A. OR2CxxA and OR2TxxA Asynchronous Memory Read During Write Operation (MA/MB Modes)

OR2CxxA Commercial: VDD = 5.0 V ± 5%, 0 °C ≤ TA ≤ 70 °C; OR2CxxA Industrial: VDD = 5.0 V ± 10%, –40 °C ≤ TA ≤ +85 °C.

OR2TxxA Commercial: VDD = 3.0 V to 3.6 V, 0 °C ≤ TA ≤ 70 °C; OR2TxxA Industrial: VDD = 3.0 V to 3.6 V, –40 °C ≤ TA ≤

+85 °C.

Speed

Parameter

Symbol

Unit

-2

-3

-4

-5

-6

-7

Min Max Min Max Min Max Min Max Min Max Min Max

Read During Write Operation

(TJ = 85 °C, VDD = min):

Write Enable (WREN) to PFU Output Delay

(A4/B4 to F[3:0])

Write-port Enable (WPE) to PFU Output

Delay (C0 to F[3:0])

MEM*_WRDEL

MEM*_PWRDEL

—

—

—

7.0

9.0

5.0

—

—

—

4.9

6.4

3.6

—

—

—

4.8

5.8

3.1

—

—

—

3.9

4.7

2.5

—

—

—

4.0

4.7

2.5

—

—

—

3.9 ns

4.5 ns

2.2 ns

Data to PFU Output Delay (WD[3:0] to F[3:0]) MEM*_DDEL

Note: Speed grades of -5, -6, and -7 are for OR2TxxA devices only.

Table 37B. OR2TxxB Asynchronous Memory Read During Write Operation (MA/MB Modes)

OR2TxxB Commercial: VDD = 3.0 V to 3.6 V, 0 °C ≤ TA ≤ 70 °C; OR2TxxB Industrial: VDD = 3.0 V to 3.6 V, –40 °C ≤ TA ≤

+85°C.

Speed

Parameter

Symbol

Unit

-7

-8

Min

Max

Min

Max

Read During Write Operation

(TJ = +85 °C, VDD = min):

Write Enable (WREN) to PFU Output Delay

(A4/B4 to F[3:0])

Write-port Enable (WPE) to PFU Output

Delay (C0 to F[3:0])

MEM*_WRDEL

MEM*_PWRDEL

MEM*_DDEL

—

—

—

4.5

4.6

2.7

—

—

—

3.9

4.0

2.4

ns

ns

ns

Data to PFU Output Delay (WD[3:0] to F[3:0])

Lucent Technologies Inc.

141

ETC [ ETC ]

ETC [ ETC ]