HY29F800

While the Automatic Erase algorithm is operating,

successive read cycles at any address cause

DQ[6] to toggle. DQ[6] stops toggling when the

erase operation is complete or when the device is

placed in the Erase Suspend mode. The host may

use DQ[2] to determine which sectors are erasing

or erase-suspended (see below). After an Erase

command sequence is written, if all sectors se-

lected for erasing are protected, DQ[6] toggles for

approximately 100 µs, then returns to reading ar-

ray data. If at least one selected sector is not

protected, the Automatic Erase algorithm erases

the unprotected sectors, and ignores the selected

sectors that are protected.

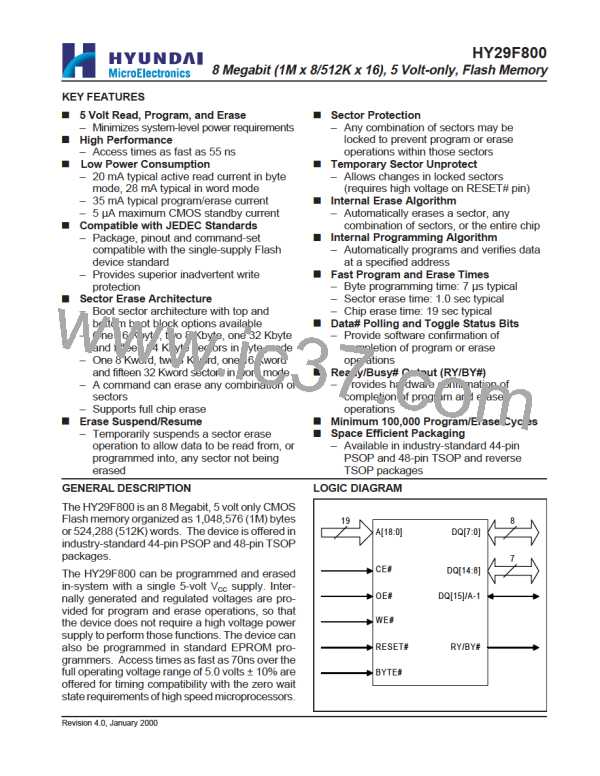

START

Read DQ[7:0]

at Valid Address (Note 1)

Test for DQ[7] = 1?

for Erase Operation

DQ[7] = Data?

NO

YES

NO

DQ[5] = 1?

YES

DQ[2] - Toggle Bit II

Read DQ[7:0]

at Valid Address (Note 1)

Toggle Bit II, DQ[2], when used with DQ[6], indi-

cates whether a particular sector is actively eras-

ing or whether that sector is erase-suspended.

Toggle Bit II is valid after the rising edge of the

final WE# pulse in the command sequence. The

device toggles DQ[2] with each OE# or CE# read

cycle.

Test for DQ[7] = 1?

for Erase Operation

DQ[7] = Data?

(Note 2)

YES

NO

PROGRAM/ERASE

EXCEEDED TIME ERROR

PROGRAM/ERASE

COMPLETE

DQ[2] toggles when the host reads at addresses

within sectors that have been selected for erasure,

but cannot distinguish whether the sector is ac-

tively erasing or is erase-suspended. DQ[6], by

comparison, indicates whether the device is ac-

tively erasing or is in Erase Suspend, but cannot

distinguish which sectors are selected for erasure.

Thus, both status bits are required for sector and

mode information.

Notes:

1. During programming, the program address.

During sector erase, an address within any non-protected sector

scheduled for erasure.

During chip erase, an address within any non-protected sector.

2. Recheck DQ[7] since it may change asynchronously at the same time

as DQ[5].

Figure 7. Data# Polling Test Algorithm

Figure 8 illustrates the operation of Toggle Bits I

and II.

For both of these conditions, the host must issue

a Read/Reset command to return the device to

the Read mode.

DQ[5] - Exceeded Timing Limits

DQ[5] is set to a ‘1’ when the program or erase

time has exceeded a specified internal pulse count

limit. This is a failure condition that indicates that

the program or erase cycle was not successfully

completed. DQ[5] status is valid only while DQ[7]

or DQ[6] indicate that the Automatic Algorithm is

in progress.

DQ[3] - Sector Erase Timer

After writing a Sector Erase command sequence,

the host may read DQ[3] to determine whether or

not an erase operation has begun. When the

sector erase time-out expires and the sector erase

operation commences, DQ[3] switches from a ‘0’

to a ‘1’. Refer to the “Sector Erase Command”

section for additional information. Note that the

sector erase timer does not apply to the Chip Erase

command.

The DQ[5] failure condition will also be signaled if

the host tries to program a ‘1’ to a location that is

previously programmed to ‘0’, since only an erase

operation can change a ‘0’ to a ‘1’.

After the initial Sector Erase command sequence

is issued, the system should read the status on

Rev. 4.0/Jan. 00

17

ETC [ ETC ]

ETC [ ETC ]