NT5DS32M4AT

NT5DS16M8AT

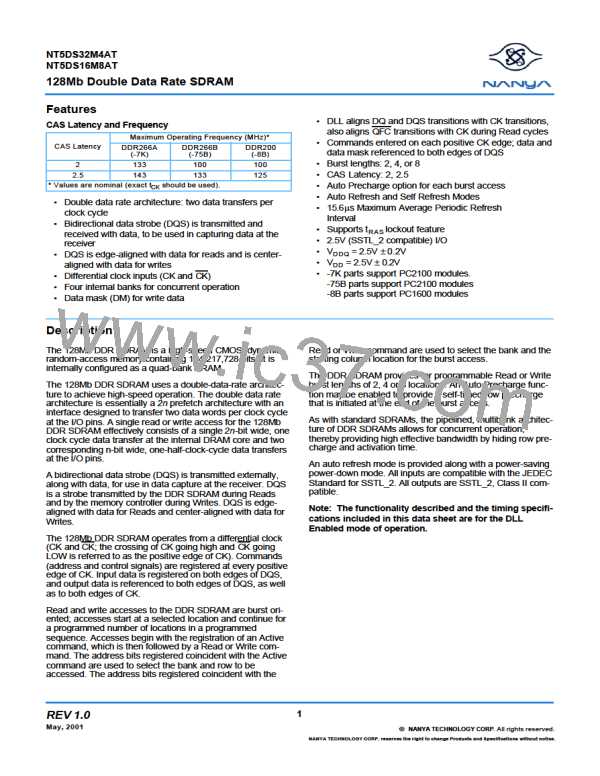

128Mb Double Data Rate SDRAM

Capacitance

Parameter

Input Capacitance: CK, CK

Symbol

Min.

2.0

Max.

3.0

Units

pF

Notes

CI

1

1

1

Delta Input Capacitance: CK, CK

delta CI

0.25

pF

1

Input Capacitance: All other input-only pins (except DM)

Delta Input Capacitance: All other input-only pins (except DM)

Input/Output Capacitance: DQ, DQS, DM

CI

2.0

4.0

2.0

3.0

0.5

5.0

0.5

4.0

pF

pF

pF

pF

pF

1

1

2

delta CI

2

C

1, 2

1

IO

Delta Input/Output Capacitance: DQ, DQS, DM

Output Capacitance: QFC

delta C

IO

CO

1

1

1. V

= V

= 2.5V ± 0.2V (minimum range to maximum range), f = 100MHz, T = 25°C, VO

= V

, VO

=0.2V.

Peak -Peak

DDQ

DD

A

DC

DDQ/2

2. Although DM is an input-only pin, the input capacitance of this pin must model the input capacitance of the DQ and DQS pins. This is

required to match input propagation times of DQ, DQS and DM in the system.

DC Electrical Characteristics and Operating Conditions

(0°C £ TA £ 70°C; VDDQ = 2.5V ± 0.2V, VDD = + 2.5V ± 0.2V, see AC Characteristics)

Symbol

Parameter

Min

2.3

2.3

Max

2.7

Units

Notes

V

Supply Voltage

V

V

1

1

DD

V

I/O Supply Voltage

2.7

DDQ

Supply Voltage

I/O Supply Voltage

V

, V

0

0

V

SS

SSQ

V

I/O Reference Voltage

0.49 x V

0.51 x V

DDQ

V

V

V

V

V

V

1, 2

1, 3

1

REF

DDQ

V

I/O Termination Voltage (System)

V

V

- 0.04

+ 0.15

V

+ 0.04

+ 0.3

TT

REF

REF

REF

V

V

V

V

Input High (Logic1) Voltage

V

IH(DC)

IL(DC)

IN(DC)

ID(DC)

DDQ

Input Low (Logic0) Voltage

- 0.3

V

- 0.15

1

REF

Input Voltage Level, CK and CK Inputs

Input Differential Voltage, CK and CK Inputs

V-I Matching Pullup Current to Pulldown Current Ratio

- 0.3

0.30

0.71

V

+ 0.3

+ 0.6

1

DDQ

DDQ

V

1, 4

5

VI

1.4

Ratio

Input Leakage Current

I

- 5

- 5

5

5

mA

mA

1

1

I

Any input 0V £ V £ V ; (All other pins not under test = 0V)

IN

DD

Output Leakage Current

(DQs are disabled; 0V £ V

I

OZ

£ V

DDQ

out

I

I

Output Current: Nominal Strength Driver

- 16.8

OH

OL

High current (V

Low current (V

= V

-0.373V, min V

, min V )

TT

mA

1

OUT

DDQ

REF

16.8

= 0.373V, max V

, max V

REF

)

OUT

TT

1. Inputs are not recognized as valid until V

stabilizes.

REF

2.

V

is expected to be equal to 0.5 V

of the transmitting device, and to track variations in the DC level of the same. Peak-to-peak

DDQ

REF

noise on V

may not exceed ± 2% of the DC value.

REF

3.

4.

V

is not applied directly to the device. V is a system supply for signal termination resistors, is expected to be set equal to V

, and

TT

TT

REF

must track variations in the DC level of V

.

REF

V

is the magnitude of the difference between the input level on CK and the input level on CK

ID

5. The ratio of the pullup current to the pulldown current is specified for the same temperature and voltage, over the entire tempera-ture and

voltage range, for device drain to source voltages for 0.25 volts to 1.0 volts. For a given output, it represents the maximum difference

between pullup and pulldown drivers due to process variation.

51

REV 1.0

May, 2001

©

NANYA TECHNOLOGY CORP. All rights reserved.

NANYA TECHNOLOGY CORP. reserves the right to change Products and Specifications without notice.

ETC [ ETC ]

ETC [ ETC ]