Advance Information MT88E46

immediately become the ACK-Sender, go off

hook no later than 20ms after the start of the

line HIGH state, complete the CAS-ACK

handshake, and remain as ACK-Sender for the

remainder of the call. This situation may

happen if the designated ACK-Sender is not

MEI compliant.

The interface is specifically designed for the 1200

baud rate and is consisted of 3 signals: DATA, DCLK

(Data Clock) and DR (Data Ready). DATA is an

output pin. DCLK is an input output pin. DR uses the

dual purpose output pin DR/DET. When FSK is

selected it is the DR signal.

•

An MEI compliant CPE that is not the

designated ACK-Sender or the Backup ACK-

Sender but which is off hook at the time of the

CAS, shall monitor the line for a line HIGH state

lasting a minimum of 30ms. Once this condition

has been detected, the CPE shall immediately

become the ACK-Sender, go off hook no later

than 35ms after the start of the line HIGH state,

complete the CAS-ACK handshake, and remain

as ACK-Sender for the duration of the call. This

situation can happen if the designated ACK-

Sender and the Backup ACK-Sender are not

MEI compliant.

Two FSK interface modes (modes 0 and 1) are

selectable via the CB0 pin. In mode 0, the FSK bit

stream is output directly. In mode 1, the data byte

and the trailing stop bit are stored in a 9 bit buffer. If

mode 1 is used, the CB0 pin can be connected to

Vdd. If mode 0 is used and full chip power down is

not required, the CB0 pin can be connected to Vss.

In Bellcore’s off hook protocol, a Type 2 CPE should

restore the voicepath within 50ms after the end of

the FSK signal. Due to noise, end of carrier detection

is not always reliable. The TIA/EIA-777 standard

requires the CPE to detect the end of FSK when any

one of the following occurs:

•

After going off hook the ACK-Sender shall

begin transmission of the ACK no earlier than

30ms and no later than 40ms after the leading

edge of the line HIGH voltage transition.

•

•

absence of carrier signal or,

more than five framing errors (trailing stop bit a

0 instead of a 1) have been detected in the FSK

message or,

After the ACK-Sender or Backup ACK-Sender

detected CAS, it must monitor the line for the line

HIGH state, which can happen only if all off hook

CPEs also detected CAS. Hence if the ACK-Sender

or Backup ACK-Sender is an on hook CPE, even if it

falsely detected CAS, talkoff can occur only if all off

hook CPEs also falsely detected CAS. Thus in the

situation where the ACK-Sender or Backup ACK-

Sender is an on hook CPE using the MT88E46 on

hook mode detection algorithm, talkoff protection is

provided by the off hook CPEs. The on hook mode

has been optimized to be more talkdown immune so

that in this situation the on hook CPE will be

successful in fulfilling its ACK-Sender or Backup

ACK-Sender responsibility.

•

more than 150ms of continuous mark signal or

space signal has been detected.

FSK Data Interface Mode 0 - Bit Stream Mode

This mode is selected when the CB0 pin is low. In

this mode the FSK data is output directly to the DATA

pin. DCLK and DR are timing signal outputs (see

Figure 14).

For each received stop and start bit sequence, the

MT88E46 outputs a fixed frequency clock string of 8

pulses at the DCLK pin. Each DCLK rising edge

occurs in the middle of a DATA bit of the FSK byte.

DCLK is not generated for the start and stop bits.

Consequently, DCLK will clock only valid data into a

peripheral device such as a serial to parallel shift

register or into a microcontroller. The MT88E46 also

outputs an end of word pulse DR (Data Ready). DR

goes low for half a nominal bit time at the beginning

of the trailing stop bit. It can be used to interrupt a

microcontroller or cause a serial to parallel converter

to parallel load its data into the microcontroller. If a

shift register is not used, DCLK and DATA may

occupy 2 bits of a microcontroller’s input port. The

microcontroller polls the input port and saves the

DATA bit when DCLK changes from low to high.

When DR goes low, the word may then be

assembled from the last 8 saved bits.

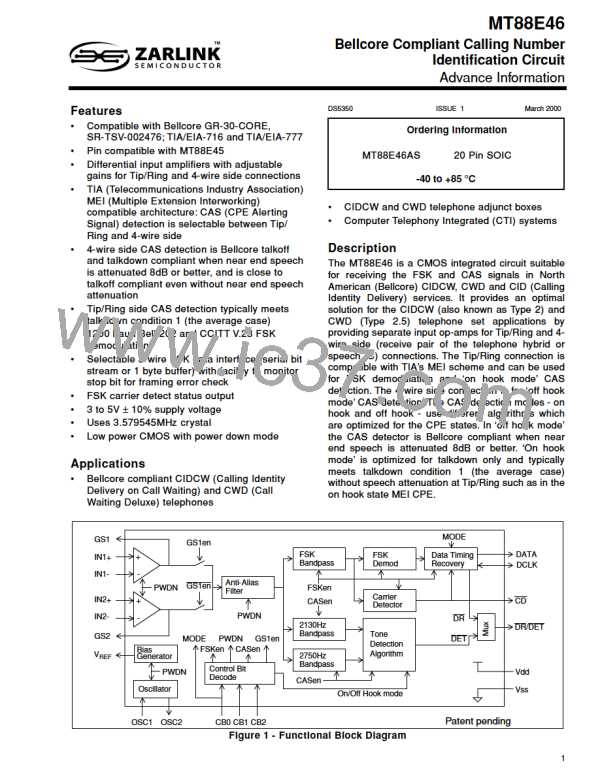

FSK Demodulation

The FSK demodulator is compatible with Bellcore

SR-TSV-002476, TIA/EIA-716 and TIA/EIA-777

standards. It is capable of both Bell 202 and CCITT

V.23 formats transparently. FSK demodulation is

available at the GS1 input op-amp only.

FSK Data Interface

The MT88E46 provides a powerful dual mode 3-wire

interface so that the data bytes in the demodulated

FSK bit stream can be extracted without the need

either for an external UART or for the CPE’s

microcontroller to perform the function in software.

9

ZARLINK [ ZARLINK SEMICONDUCTOR INC ]

ZARLINK [ ZARLINK SEMICONDUCTOR INC ]