Product Preview

WM8983

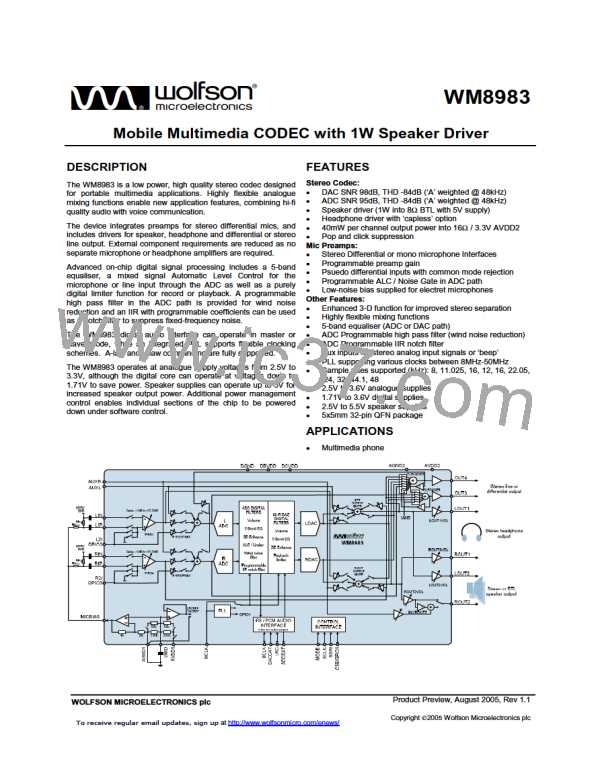

INTERNAL POWER ON RESET CIRCUIT

Figure 8 Internal Power on Reset Circuit Schematic

The WM8983 includes an internal Power-On-Reset Circuit, as shown in Figure 8, which is used reset

the digital logic into a default state after power up. The POR circuit is powered from AVDD1 and

monitors DCVDD. It asserts PORB low if AVDD1 or DCVDD is below a minimum threshold.

Figure 9 Typical Power up Sequence Where AVDD1 is Powered Before DCVDD

Figure 9 shows a typical power-up sequence where AVDD1 comes up first. When AVDD1 goes

above the minimum threshold, Vpora, there is enough voltage for the circuit to guarantee PORB is

asserted low and the chip is held in reset. In this condition, all writes to the control interface are

ignored. Now AVDD1 is at full supply level. Next DCVDD rises to Vpord_on and PORB is released high

and all registers are in their default state and writes to the control interface may take place.

On power down, where AVDD1 falls first, PORB is asserted low whenever AVDD1 drops below the

minimum threshold Vpora_off

.

PP Rev 1.1 August 2005

17

w

WOLFSON [ WOLFSON MICROELECTRONICS PLC ]

WOLFSON [ WOLFSON MICROELECTRONICS PLC ]