VITESSE

SEMICONDUCTOR CORPORATION

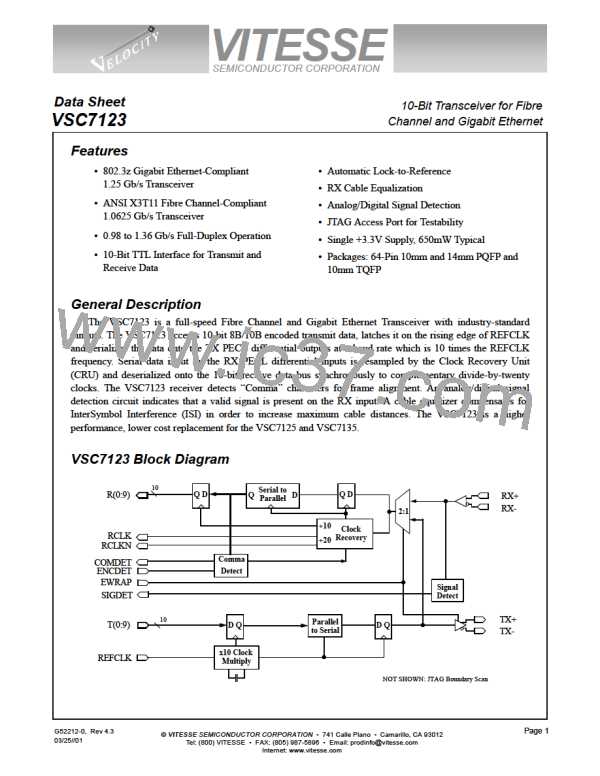

Data Sheet

10-Bit Transceiver for Fibre

Channel and Gigabit Ethernet

VSC7123

Signal Detection

The receiver has an output, SIGDET, indicating, when HIGH, that the RX input contains a valid Fibre

Channel or Gigabit Ethernet signal. A combination of one analog and three digital checks are used to determine

if the incoming signal contains valid data. SIGDET is updated every four RCLKs. If during the current period,

all the four criteria are met, SIGDET will be HIGH during the next 4 RCLK period. If during the current period,

any of the four criteria is not met, SIGDET will be LOW during the next 4 RCLK period.

1) Analog transition detection is performed on the input to verify that the signal swings are of adequate

amplitude. The RX+/- input buffer contains a differential voltage comparator which will go HIGH if the

differential peak-to-peak amplitude is greater than 400mV or LOW if under 200mV. If the amplitude is

between 200mV and 400mV, the output is indeterminate.

2) Data on R(0:9) is monitored for all zeros (0000000000). If this pattern is encountered during the current

RCLK interval, the SIGDET output will go LOW during the next four RCLK interval.

3) Data on R(0:9) is monitored for all ones (1111111111). If this pattern is encountered during the current

RCLK interval, the SIGDET output will go LOW during the next four RCLK interval.

4) Data on R(0:9) is monitored for K28.5- (0011111010). Unlike previous patterns, the interval during which

a K28.5- must occur is 64K+24 10-bit characters in length. Valid Fibre Channel or Gigabit Ethernet data

will contain a K28.5- character during any period of this length. If a K28.5- is not detected during the

monitoring period, SIGDET will go LOW during the next period.

The behavior of SIGDET is affected by EWRAP and ENCDET as shown in Table 1.

Table 1: Signal Detect Behavior

Transition

Detect

All Zeros/

All Ones

K28.5

Presence

EWRAP

ENCDET

COMDET

Mode

0

0

1

1

0

1

0

1

Disabled

Enabled

Disabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Enabled

Disabled

Disabled

Enabled

Disabled

Disabled

Disabled

Normal

SIGDET ignores commas

Rollback

Loopback

Note: COMDET, RCLK, RCLKN and R(0:9) are unaltered by SIGDET.

JTAG Access Port

A JTAG Access Port is provided to assist in board-level testing. Through this port, most pins can be

accessed or controlled and all TTL outputs can be tri-stated. A full description of the JTAG functions on this

device is available in “VSC7123/VSC7133 JTAG Access Port Functionality.”

G52212-0, Rev 4.3

03/25//01

Page 5

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VITESSE [ VITESSE SEMICONDUCTOR CORPORATION ]

VITESSE [ VITESSE SEMICONDUCTOR CORPORATION ]