VITESSE

SEMICONDUCTOR CORPORATION

Data Sheet

10-Bit Transceiver for Fibre

Channel and Gigabit Ethernet

VSC7123

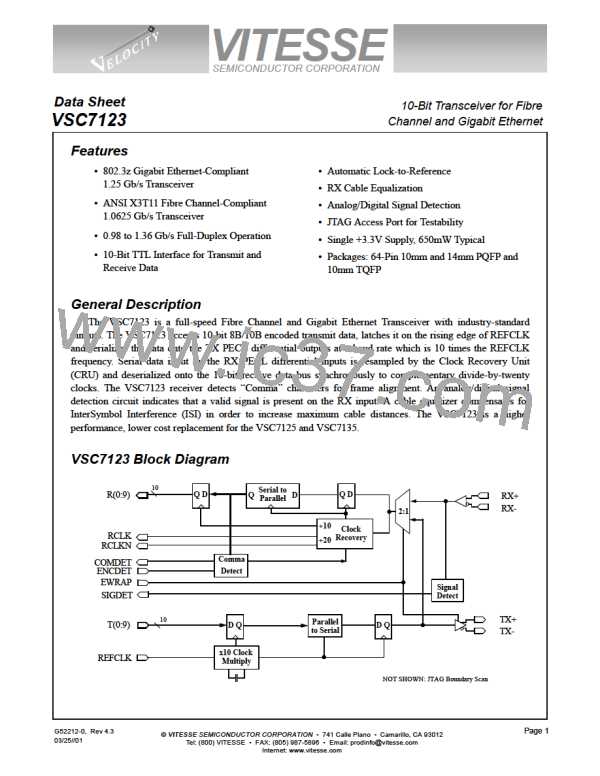

Figure 5: Receive Timing Waveforms

T4

RCLK

T

3

RCLKN

R(0:9)

T2

T1

Data Valid

Data Valid

Data Valid

Table 3: Receive AC Characteristics

Parameters

Description

Min.

Max.

Units

Conditions

At 1.0625Gb/s

TTL Outputs Valid prior to

RCLK/RCLKN rise

4.0

3.0

—

—

T1

ns

ns

At 1.25Gb/s

TTL Outputs Valid after

RCLK or RCLKN rise

3.0

2.0

—

—

At 1.0625Gb/s

At 1.25Gb/s

T2

T3

Delay between rising edge of

RCLK to rising edge of

RCLKN

10 x TRX

-500

10 x TRX

+500

TRX is the bit period of the

incoming data on Rx.

ps

ps

ns

Period of RCLK and

RCLKN

1.98 x

TREFCLK

2.02 x

TREFCLK

Whether or not locked to

serial data.

T4

R(0:9), COMDET, SIGDET,

RCLK and RCLKN rise and

fall time

Between VIL(MAX) and

VIH(MIN), into 10pf load.

TR, TF

—

2.4

bc

ns

bc = bit clock

ns = nano second

RLAT

Latency from RX to R(0:9)

Data acquisition lock time

12 bc + 1 ns

13 bc + 9 ns

1400

8B/10B IDLE pattern.

bc = bit clocks

(1)

TLOCK

—

bc

NOTE: (1) Probability of recovery for data acquisition is 95% per Section 5.3 of FC-PH rev. 4.3.

G52212-0, Rev 4.3

03/25//01

Page 7

© VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012

Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com

Internet: www.vitesse.com

VITESSE [ VITESSE SEMICONDUCTOR CORPORATION ]

VITESSE [ VITESSE SEMICONDUCTOR CORPORATION ]