UCC28610

SLUS888C–JANUARY 2009–REVISED SEPTEMBER 2009 ......................................................................................................................................... www.ti.com

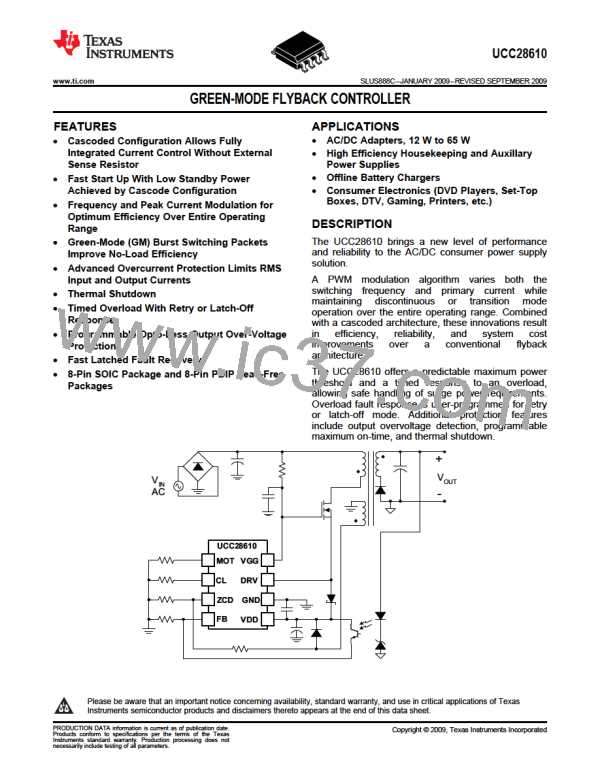

Block Diagram

V GG

VDD

Fault Latch

Reset

LDO

Reg

Switch

13V

+

5

VGG

+

10V/6V

VGG

14V

2V

Shunt

8

HS

VDD

Drive

UVLO

+

10V/8V

Enable

PWM

I

FB

1

FB

IFB

IFB

6

DRV

Freq. Modulator

1/tS

Feedback

Processing

tS

Modulators

Green-mode

0m A < IFB < 200mA

IFB > 200mA

IFB = 0

IFB

Enable

PWM

Overload

VGATE

D

Q

Driver

Zero Current

Detect

5

ZCD

7.5k

Q

W

Bulk

Discharge

OV

Output

Voltage

Sense

5V

Fault

7

GND

Maximum On Time

& Fault Response

Control

IFB

Current

Modulator

Fault Timing

& Control

I

MOT

Fault

V GATE

IP

Latch or

Retry

3

CL

3V

+

IFB

Fault Latch

Reset

Shutdown

and

Restart

UVLO

1V

4

MOT

Thermal

Shutdown

UCC28610

Block Diagram

Figure 19. Symplified Block Diagram

12

Submit Documentation Feedback

Copyright © 2009, Texas Instruments Incorporated

Product Folder Link(s): UCC28610

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]