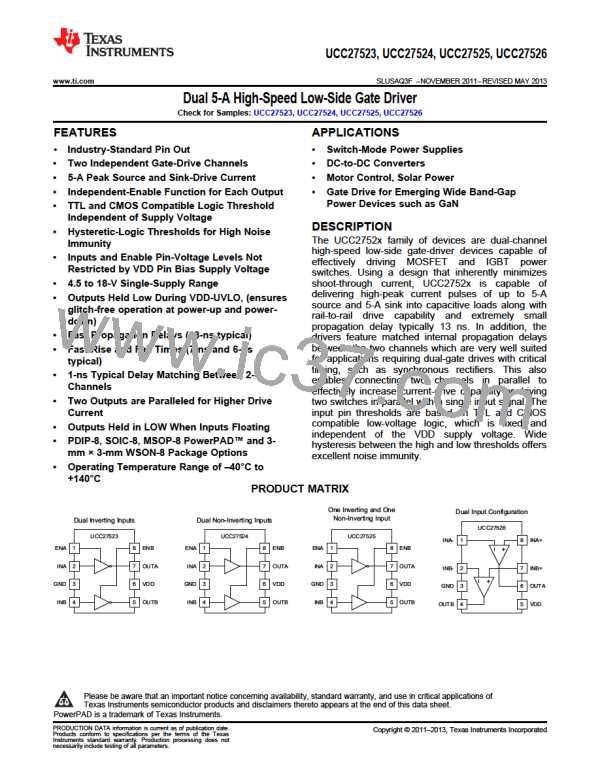

UCC27523, UCC27524, UCC27525, UCC27526

SLUSAQ3F –NOVEMBER 2011–REVISED MAY 2013

www.ti.com

THERMAL INFORMATION

UCC27523,

UCC27524,

UCC27525

UCC27523,

UCC27524,

UCC27525

MSOP (DGN)(1)

THERMAL METRIC

UNITS

SOIC (D)

8 PINS

130.9

80.0

8 PINS

71.8

65.6

7.4

θJA

Junction-to-ambient thermal resistance(2)

Junction-to-case (top) thermal resistance(3)

Junction-to-board thermal resistance(4)

Junction-to-top characterization parameter(5)

Junction-to-board characterization parameter(6)

Junction-to-case (bottom) thermal resistance(7)

θJCtop

θJB

71.4

°C/W

ψJT

21.9

7.4

ψJB

70.9

31.5

19.6

θJCbot

n/a

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as

specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-

standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB

temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter, ψJT, estimates the junction temperature of a device in a real system and is extracted

from the simulation data for obtaining θJA, using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter, ψJB, estimates the junction temperature of a device in a real system and is extracted

from the simulation data for obtaining θJA , using a procedure described in JESD51-2a (sections 6 and 7).

(7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific

JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

Spacer

THERMAL INFORMATION

UCC27524

UCC27523,

UCC27524,

UCC27525,

UCC27526

THERMAL METRIC

UNITS

PDIP (P)

8 PINS

62.1

WSON (DSD)(1)

8 PINS

46.7

46.7

22.4

0.7

θJA

Junction-to-ambient thermal resistance(2)

Junction-to-case (top) thermal resistance(3)

Junction-to-board thermal resistance(4)

Junction-to-top characterization parameter(5)

Junction-to-board characterization parameter(6)

Junction-to-case (bottom) thermal resistance(7)

θJCtop

θJB

52.7

39.1

°C/W

ψJT

31.0

ψJB

39.1

22.6

9.5

θJCbot

n/a

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

(2) The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as

specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC-

standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB

temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter, ψJT, estimates the junction temperature of a device in a real system and is extracted

from the simulation data for obtaining θJA, using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter, ψJB, estimates the junction temperature of a device in a real system and is extracted

from the simulation data for obtaining θJA , using a procedure described in JESD51-2a (sections 6 and 7).

(7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific

JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

Spacer

4

Submit Documentation Feedback

Copyright © 2011–2013, Texas Instruments Incorporated

Product Folder Links: UCC27523, UCC27524, UCC27525, UCC27526

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]