TPS7A39

www.ti.com.cn

ZHCSGP0A –JULY 2017–REVISED SEPTEMBER 2017

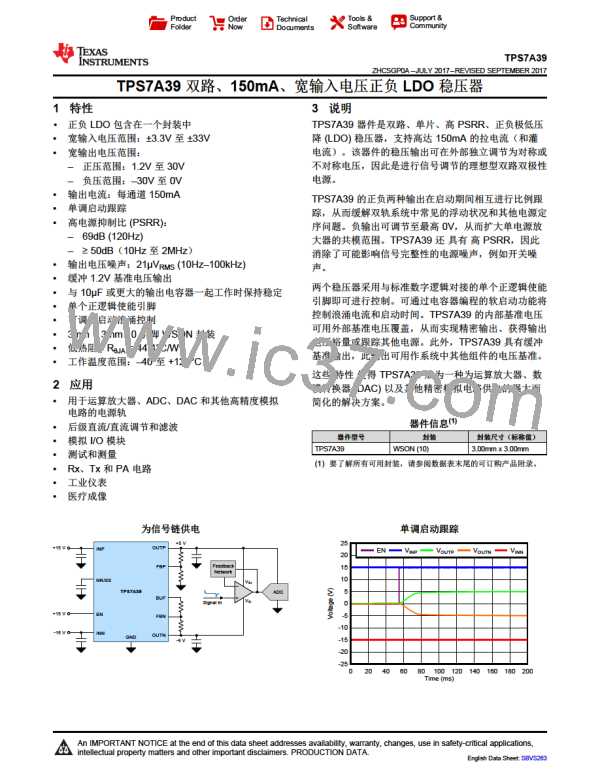

7.3.4.2.1 Enable (EN)

The enable signal (VEN) is an active-high digital control that enables the LDO when the enable voltage is past the

rising threshold (VEN ≥ VIH(EN)) and disables the LDO when the enable voltage is below the falling threshold (VEN

≤ VIL(EN)). The exact enable threshold is between VIH(EN) and VIL(EN) because EN is a digital control. In

applications that do not use the enable control, connect EN to VINP

.

A slow VINx ramp directly connecting EN to VINP can cause the start-up tracking to move out of specification.

Under slow ramp conditions, use a resistor divider from VINP to ensure start-up tracking.

7.3.4.2.2 Undervoltage Lockout (UVLO) Control

The UVLO circuit responds quickly to glitches on the input supplies and attempts to disable the output of the

device if either of these rails collapse.

As a result of the fast response time of the input supply UVLO circuit, fast and short line transients well below the

input supply UVLO falling threshold (brownouts) can cause momentary glitches during the edges of the transient.

These glitches are typical in most LDOs. The local input capacitance prevents severe brown-outs in most

applications; see the Undervoltage Lockout (UVLOx) Control section for more details. Fast line transients can

cause the outputs to momentarily shut off, and can be mitigated through using the recommended 10-µF input

capacitor. If this becomes a problem in the system, increasing the input capacitance prevents these glitches from

occurring.

版权 © 2017, Texas Instruments Incorporated

23

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]