TPS40210-Q1, TPS40211-Q1

SLVS861D –AUGUST 2008–REVISED APRIL 2010

www.ti.com

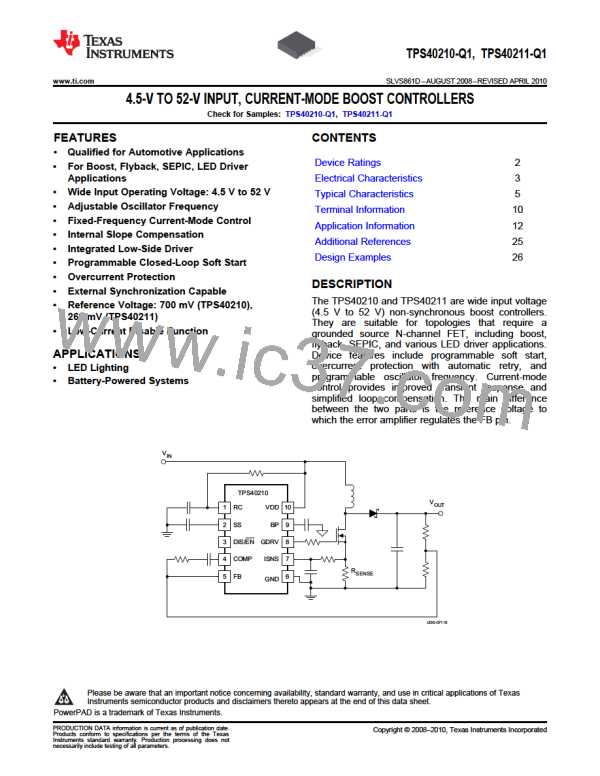

TEST DATA

GAIN AND PHASE

vs

FET Vds and Vgs VOLTAGES

vs

FREQUENCY

TIME

80

180

135

90

V

V

I

= 8 V

IN

OUT

= 24 V

60

GDRV

(5 V/ div)

= 2 A

Phase

OUT

40

20

0

45

0

Gain

-20

-45

-90

-135

-180

FET Vds

(20 V/ div)

-40

-60

-80

100

1000

10 k 100 k

– Frequency – Hz

1 M

f

SW

T – Time – 400 ns

Figure 31.

Figure 32.

EFFICIENCY

POWER LOSS

vs

vs

LOAD CURRENT

LOAD CURRENT

100

6

5

V

= 8 V

V

(V)

14

12

8

V

(V)

IN

IN

IN

V

= 14V

98

96

IN

14

12

8

94

92

90

4

3

2

V

= 12 V

IN

V

= 12 V

IN

88

86

V

= 8 V

IN

V

= 14 V

IN

84

82

80

1

0

0

0.5

1.0 1.5

– Load Current – A

2.0

2.5

0

0.5

1.0 1.5

– Load Current – A

2.0

2.5

I

I

LOAD

LOAD

Figure 33.

Figure 34.

32

Submit Documentation Feedback

Copyright © 2008–2010, Texas Instruments Incorporated

Product Folder Link(s): TPS40210-Q1 TPS40211-Q1

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]