ꢀ ꢁꢂ ꢃ ꢄ ꢅ ꢆꢇ ꢀꢁ ꢂ ꢃ ꢄ ꢅ ꢈ

ꢂ

ꢀ

ꢁ

ꢂ

ꢃ

ꢄ

ꢅ

ꢉꢇ

ꢀ

ꢁ

ꢃ

ꢄ

ꢅ

ꢄ

www.ti.com

SLES081A − JUNE 2003 – REVISED MAY 2004

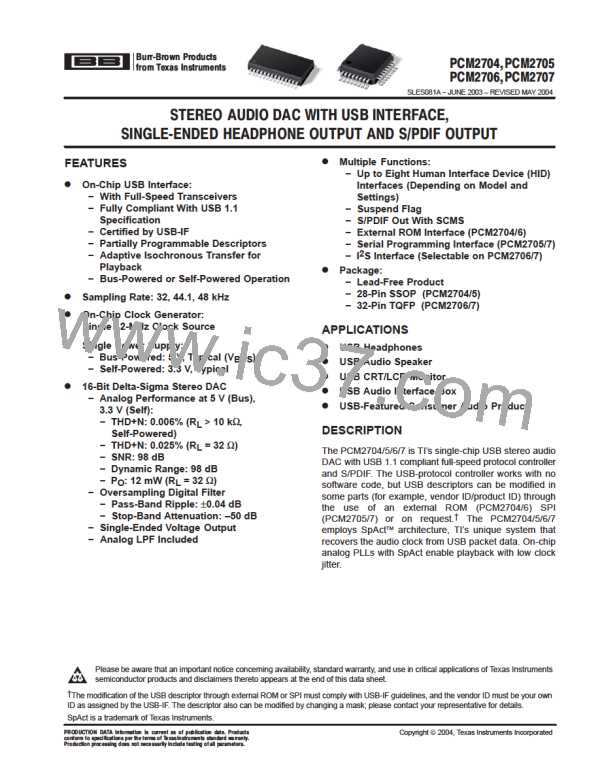

(1) Single Write Operation

16-Bits

MS

MC

MD

MSB

LSB

MSB

(2) Continuous Write Operation

16-Bits x N Frames

MS

MC

MD

MSB

LSB

MSB

LSB

MSB

LSB

N Frames

Figure 27. SPI Write Operation

SPI REGISTER (PCM2705/7)

B15

B14

B13

B12

B11

B10

B9

B8

B7

B6

B5

B4

B3

B2

B1

B0

D7

0

0

0

0

ST

0

ADDR

0

D0

D1

D2

D3

D4

D5

D6

D[7:0]

Function of the lower 8 bits depends on the value of the ST (B11) bit.

ST = 0 (HID status write)

D7

D6

D5

D4

D3

D2

D1

D0

Reports MUTE HID status to the host (active high)

Reports volume-up HID status to the host (active high)

Reports volume-down HID status to the host (active high)

Reports next-track HID status to the host (active high)

Reports previous-track HID status to the host (active high)

Reports stop HID status to the host (active high)

Reports play/pause HID status to the host (active high)

Reports extended command status to the host (active high)

ST = 1 (ROM data write)

D[7:0] Internal descriptor ROM data

ADDR

Starts write operation for internal descriptor reprogramming (active high)

456 bits of ROM data, (described in the External ROM Example section) must be provided when this bit is asserted.

To set ADDR high, ST must be set low. Note that the lower 8 bits are still active when ST is set low.

ST

Determines the function of the lower 8-bit data as follows

0: HID status write

1: Descriptor ROM data write

24

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]