CC2640R2L

ZHCSRK4A –APRIL 2020 –REVISED SEPTEMBER 2020

www.ti.com.cn

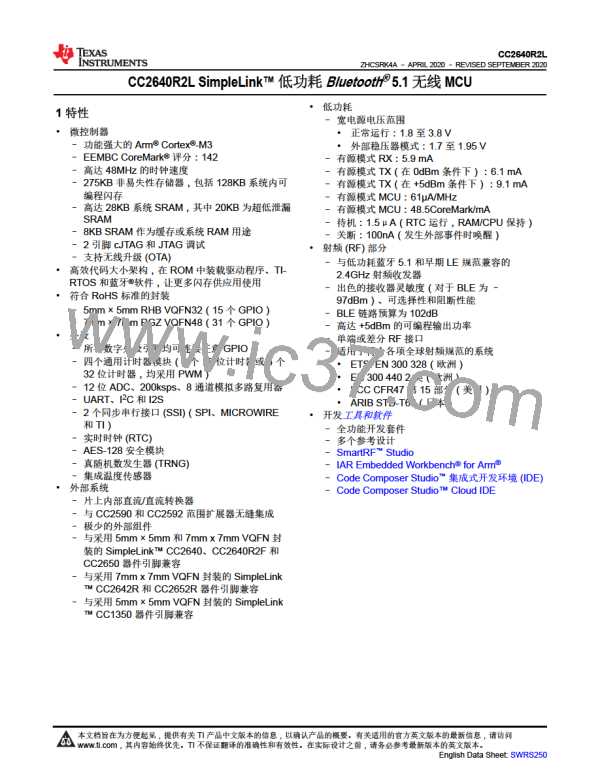

7.4 Signal Descriptions –RHB Package

表7-2. Signal Descriptions –RHB Package

NAME

NO.

17

12

6

TYPE

DESCRIPTION

DCDC_SW

DCOUPL

DIO_0

Power

Output from internal DC/DC(1)

1.27-V regulated digital-supply decoupling(2)

GPIO

Power

Digital I/O

Digital I/O

Digital I/O

Digital I/O

Digital I/O

Digital I/O

Digital I/O

DIO_1

7

GPIO

DIO_2

8

GPIO, high-drive capability

GPIO, high-drive capability

GPIO, high-drive capability

GPIO, High drive capability, JTAG_TDO

GPIO, High drive capability, JTAG_TDI

DIO_3

9

DIO_4

10

15

16

20

21

22

23

24

25

26

27

13

14

19

DIO_5

DIO_6

DIO_7

Digital/Analog I/O GPIO, Analog

Digital/Analog I/O GPIO, Analog

Digital/Analog I/O GPIO, Analog

Digital/Analog I/O GPIO, Analog

Digital/Analog I/O GPIO, Analog

Digital/Analog I/O GPIO, Analog

Digital/Analog I/O GPIO, Analog

Digital/Analog I/O GPIO, Analog

DIO_8

DIO_9

DIO_10

DIO_11

DIO_12

DIO_13

DIO_14

JTAG_TMSC

JTAG_TCKC

RESET_N

Digital I/O

Digital I/O

Digital input

JTAG TMSC, high-drive capability

JTAG TCKC(3)

Reset, active-low. No internal pullup.

Negative RF input signal to LNA during RX,

Negative RF output signal to PA during TX

RF_N

RF_P

2

1

RF I/O

RF I/O

Positive RF input signal to LNA during RX,

Positive RF output signal to PA during TX

RX_TX

3

RF I/O

Power

Optional bias pin for the RF LNA

VDDR

29

32

28

11

18

4

1.7-V to 1.95-V supply, typically connect to output of internal DC/DC(4) (2)

1.7-V to 1.95-V supply, typically connect to output of internal DC/DC(2) (5)

1.8-V to 3.8-V main chip supply(1)

VDDR_RF

VDDS

Power

Power

VDDS2

Power

1.8-V to 3.8-V GPIO supply(1)

VDDS_DCDC

X32K_Q1

X32K_Q2

X24M_N

X24M_P

EGP

Power

1.8-V to 3.8-V DC/DC supply

Analog I/O

Analog I/O

Analog I/O

Analog I/O

Power

32-kHz crystal oscillator pin 1

5

32-kHz crystal oscillator pin 2

30

31

24-MHz crystal oscillator pin 1

24-MHz crystal oscillator pin 2

Ground –exposed ground pad

(1) See technical reference manual (listed in 节11.3) for more details.

(2) Do not supply external circuitry from this pin.

(3) For design consideration regarding noise immunity for this pin, see the JTAG Interface chapter in the CC13x0, CC26x0 SimpleLink™

Wireless MCU Technical Reference Manual

(4) If internal DC/DC is not used, this pin is supplied internally from the main LDO.

(5) If internal DC/DC is not used, this pin must be connected to VDDR for supply from the main LDO.

Copyright © 2023 Texas Instruments Incorporated

10

Submit Document Feedback

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]