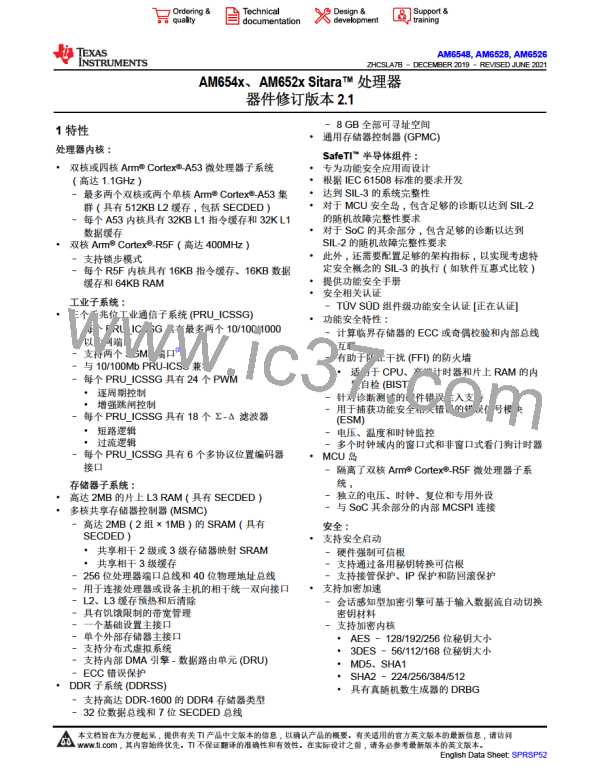

AM6548, AM6528, AM6526

ZHCSLA7B –DECEMBER 2019 –REVISED JUNE 2021

www.ti.com.cn

表6-8. DDRSS0 Signal Descriptions (continued)

PIN TYPE

SIGNAL NAME [1]

DESCRIPTION [2]

DDRSS Calibration Resistor(2)

BALL [4]

[3]

DDR_VTP

A

F13

(1) This pin is intended for observation purpose only. No external voltage should be applied to this pin.

(2) An external 240Ω ±1% resistor must be connected between this pin and VSS. No external voltage should be applied to this pin.

(3) Do not connect any signal, test point, or board trace to this signal.

6.3.4.2 DDRSS Mapping

表6-9 presents DDRSS interface signal mapping per device memory type.

Note

DDR3L and LPDDR4 memory types are not supported on this SoC.

表6-9. DDRSS Signal Mapping

MEMORY TYPE

DDR4(1) (2)

A0

PIN

TYPE[3]

SIGNAL NAME [1]

DDR_AC0

BALL[4]

DDR3L(2)

A0

LPDDR4(1)

CA0_A

CA1_A

CA2_A

CA3_A

CA4_A

CA5_A

CA0_B

CA1_B

CA2_B

CA3_B

CA4_B

CA5_B

CS0_B

CKE0_B

CS1_B

CKE1_B

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

IO

A10

D9

DDR_AC1

DDR_AC2

DDR_AC3

DDR_AC4

DDR_AC5

DDR_AC6

DDR_AC7

DDR_AC8

DDR_AC9

DDR_AC10

DDR_AC11

DDR_AC12

DDR_AC13

DDR_AC14

DDR_AC15

DDR_AC16

DDR_AC17

DDR_AC18

DDR_AC19

DDR_AC20

DDR_AC21

DDR_AC22

DDR_AC23

DDR_AC24

DDR_AC25

DDR_AC26

DDR_AC27

DDR_AC28

DDR_AC29

DDR_ALERTn

A1

A1

A2

A2

C9

A3

A3

E9

A4

A4

A9

A5

A5

E8

A6

A6

F8

A7

A7

C7

A8

A8

C8

A9

A9

D7

A10

A11

A12

A13

A14

A15

WE_n

CAS_n

RAS_n

BA0

BA1

BA2

A10

E7

A11

A6

A12

F7

A13

D6

A14/WE_n

A15/CAS_n

A16/RAS_n

A17

C6

F6

E6

E5

ACT_n

BA0

D8

D10

E10

C10

F11

B10

D11

B11

C11

E11

E12

D12

D5

BA1

BG0

BG1

PAR

CS0_n

ODT0

CKE0

CS1_n

ODT1

CKE1

CS0_n

ODT0

CKE0

CS1_n

ODT1

CKE1

ALERT_n

CS0_A

CKE0_A

CS1_A

CKE1_A

Copyright © 2021 Texas Instruments Incorporated

66

Submit Document Feedback

Product Folder Links: AM6548 AM6528 AM6526

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]