ADS1274

ADS1278

SBAS367F –JUNE 2007–REVISED FEBRUARY 2011

www.ti.com

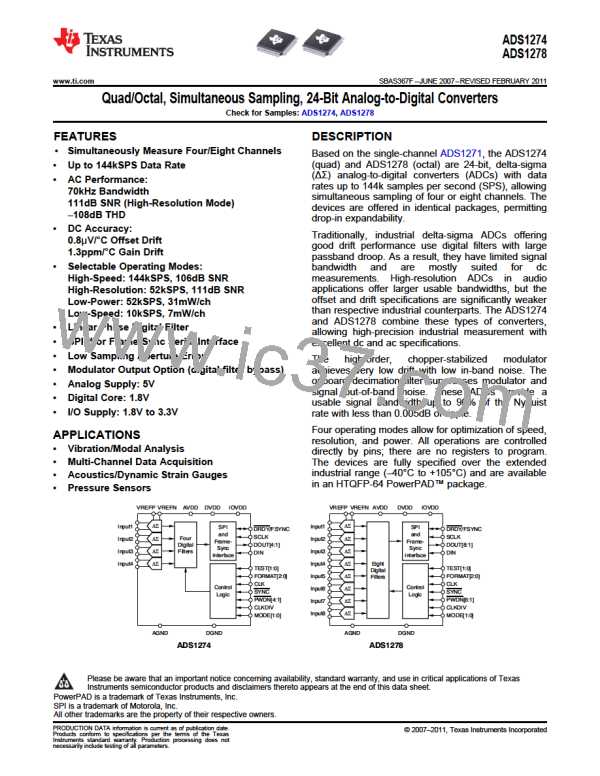

tCSHD

CLK

tSCSU

tSYN

SYNC

DRDY

tNDR

Figure 73. Synchronization Timing (SPI Protocol)

Table 11. SPI Protocol

SYMBOL

tCSHD

tSCSU

tSYN

DESCRIPTION

MIN

10

5

TYP

MAX

UNITS

CLK to SYNC hold time

SYNC to CLK setup time

Synchronize pulse width

Time for new data to be ready

ns

ns

1

CLK periods

Conversions (1/fDATA)

tNDR

129

tCSHD

CLK

tSCSU

tSYN

SYNC

FSYNC

DOUT

tNDR

Valid Data

Figure 74. Synchronization Timing (Frame-Sync Protocol)

Table 12. Frame-Sync Protocol

SYMBOL

tCSHD

tSCSU

tSYN

DESCRIPTION

MIN

10

5

TYP

MAX

UNITS

CLK to SYNC hold time

SYNC to CLK setup time

Synchronize pulse width

Time for new data to be ready(1)

ns

ns

1

CLK periods

Conversions (1/fDATA)

tNDR

127

128

(1) If SYNC is asynchronous to the FSYNC clock, then tNDR varies from 127 to 128 conversions, starting from the rising edge of SYNC. If

SYNC is made synchronous to the FSYNC clock, then tNDR is stable.

28

Submit Documentation Feedback

© 2007–2011, Texas Instruments Incorporated

Product Folder Link(s): ADS1274 ADS1278

TI [ TEXAS INSTRUMENTS ]

TI [ TEXAS INSTRUMENTS ]