SMS44

PI N DESCRI PTI ON S

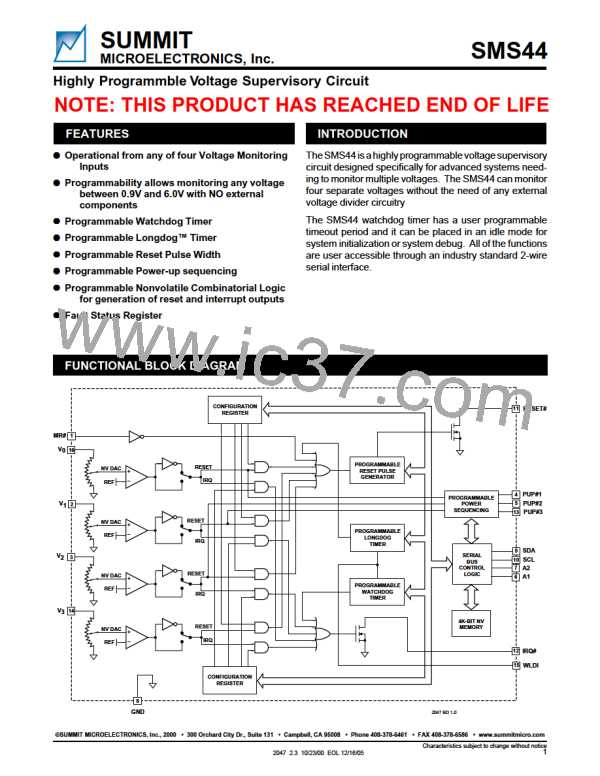

V0 through V

3

MR#

Theseinputsareusedasthevoltagemonitorinputsandas

thevoltagesupplyfortheSMS44. Internallytheyarediode

ORed and the input with the highest voltage potential will

be the default supply voltage.

t

DMRRST

t

t

RESET#

PRTO

PRTO

TheRESET#outputwillbetrueifanyoneofthefourinputs

isabove1V. However,forfulldeviceoperationatleastone

of the inputs must be at 2.7V or higher.

2047 Fig01 1.0

Fi gure 1.

RESET# Ti mi ng wi th MR#

The sensing threshold for each input is independently

programmable in 20mV increments from 0.9V to 6.0V.

Also, the occurrence of an under- or over-voltage condi-

tion that is detected as a result of the threshold setting can

be used to generate subsequent action(s), such as RE-

SET#orIRQ#. Theprogrammablenatureofthethreshold

voltage eliminates the need for external voltage divider

networks.

I RQ#

The interrupt output is an active low open-drain output. It

will be driven low whenever the watchdog timer times out

or whenever an enabled under-voltage or over-voltage

condition on a V input exists (conf i gurati on regi ster 6).

PUP#1, PUP#2 , PUP#3

V

V

t

RST

PTH

These are the power-up permitted outputs when the

SMS44isprogrammedtoprovidethesequencingofLDOs

or DC to DC converters. Each delay is independently

enabled and programmable for its duration (conf i gura-

ti on regi ster )7. If all PUP# outputs are enabled the

sequence would be as follows: V0 above threshold then

delay to PUP#1 turning on; V1 above threshold then delay

to PUP#2 turning on; V2 above threshold then delay to

PUP#3 turning on to end the sequence.

V

— V

3

0

t

D

PRTO

RESET#

I RQ#

2047 Fig02 1.1

MR#

The manual reset input always generates a RESET#

output whenever it is driven low. The duration of the

RESET# output pulse will be initiated when MR# goes low

and it will stay low for the duration of MR# low plus the

Fi gure 2 .

RESET# Ti mi ng wi th I RQ#

WLDI

programmed reset timeout period (tPRTO). If MR# is Watchdogandlongdogtimerinterruptinput. Alowtohigh

broughtlowduringapower-on-sequenceofthePUP#sthe transition on the WLDI input will clear both the watchdog

sequencewillbehaltedfortheresetduration,andwillthen and longdog timers, effectively starting a new timeout

resume from the point at which it was interrupted. If MR# period.

is low the configuration registers can be read or written to

If WLDI is stuck low and no low-to-high transition is

so long as at least one of the VX inputs is ≥2.7V.

received within the programmed tPWDTO period (pro-

grammed watch dog timeout) IRQ# will be driven low. If a

RESET#

transition is still not received within the programmed

The reset output is an active low open drain output. It will

tPLDTOperiod(programmedlongdogtimeout)RESET#will

be driven low whenever the MR# input is low or whenever

be driven low. Refer to Figure 3 for a detailed illustration.

anenabledunder-voltageorover-voltageconditionexists,

Holding WLDI high will block interrupts from occurring but

orwhenalongdogtimerexpirationexists. Thefourvoltage

will not block the longdog from timing out and generating

monitor inputs are always functioning, but their ability to

generate a reset is programmable (conf i gurati on regi s-

ter 4). Refer to figures 1 and 2 for a detailed illustration of

a reset. Refer to Figure 4 for a detailed illustration of the

relationship between IRQ#, RESET#, and WLDI.

therelationshipbetweenMR#,IRQ#,RESET#andtheVIN

levels.

SUMMIT MICROELECTRONICS, Inc.

2047 2.3 10/23/00

5

SUMMIT [ SUMMIT MICROELECTRONICS, INC. ]

SUMMIT [ SUMMIT MICROELECTRONICS, INC. ]