ST24/25C02, ST24C02R, ST24/25W02

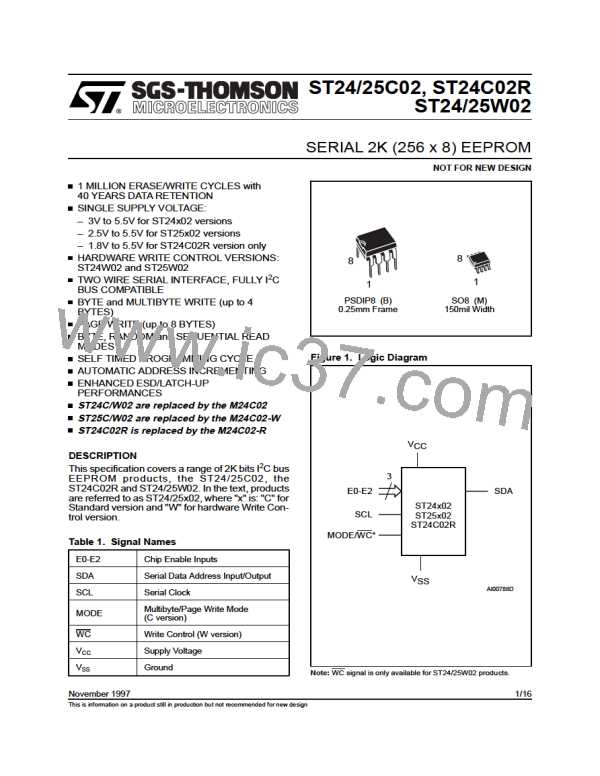

Figure 9. Write Modes Sequence with Write Control = 1 (ST24/25W02)

WC

ACK

ACK

ACK

BYTE WRITE

DEV SEL

BYTE ADDR

DATA IN

R/W

WC

ACK

ACK

ACK

PAGE WRITE

DEV SEL

BYTE ADDR

DATA IN 1

DATA IN 2

R/W

WC (cont'd)

ACK

ACK

PAGE WRITE

(cont'd)

DATA IN N

AI01101B

Sequential Read. This mode can be initiated with

either a Current Address Read or a Random Ad-

dress Read. However, in this case the master

DOES acknowledge the data byte output and the

memory continues to output the next byte in se-

quence. To terminate the stream of bytes, the

master must NOT acknowledge the last byte out-

put, but MUST generate a STOP condition. The

output data is from consecutive byte addresses,

with the internal byte address counter automat-

ically incremented after each byte output. After a

count of the last memory address, the address

counter will ’roll- over’andthememory will continue

to output data.

Acknowledge in Read Mode. In all read modes

theST24/25x02waitforan acknowledgeduringthe

9th bit time. If the master does not pull the SDAline

low during this time, the ST24/25x02 terminate the

data transfer and switches to a standby state.

11/16

STMICROELECTRONICS [ ST ]

STMICROELECTRONICS [ ST ]