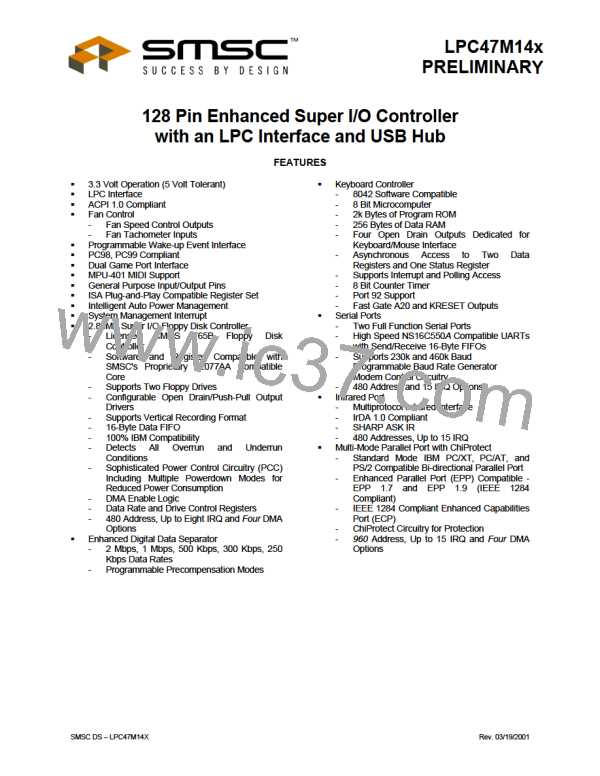

PCI_CLK

SER_IRQ

t1

t2

FIGURE 39 – SETUP AND HOLD TIME

NAME

t1

t2

DESCRIPTION

SER_IRQ Setup Time to PCI_CLK Rising

SER_IRQ Hold Time to PCI_CLK Rising

MIN

7

0

TYP

MAX

UNITS

nsec

nsec

Data

Stop (1-2 Bits)

Data (5-8 Bits)

Start

Parity

t1

TXD1, 2

FIGURE 40 – SERIAL PORT DATA

NAME

t1

DESCRIPTION

Serial Port Data Bit Time

MIN

TYP

tBR

MAX

UNITS

nsec

1

Note 1: tBR is 1/Baud Rate. The Baud Rate is programmed through the divisor latch registers. Baud Rates have

percentage errors indicated in the “Baud Rate” table in the “Serial Port” section.

VREF

2

3

VREF +/- 5%

J1X, J1Y,

J2X, J2Y

t1

FIGURE 41 – JOYSTICK POSITION SIGNAL

NAME

t1

DESCRIPTION

Rise Time to 2/3 VREF

MIN

20

TYP

MAX

UNITS

µsec

90%

10%

90%

10%

J1B1, J1B2,

J2B1, J2B2

t1

FIGURE 42 – JOYSTICK BUTTON SIGNAL

DESCRIPTION MIN

t2

NAME

TYP

MAX

10

UNITS

µsec

t1, t2 Button Fall/Rise Time

SMSC DS – LPC47M14X

Page 197

Rev. 03/19/2001

SMSC [ SMSC CORPORATION ]

SMSC [ SMSC CORPORATION ]