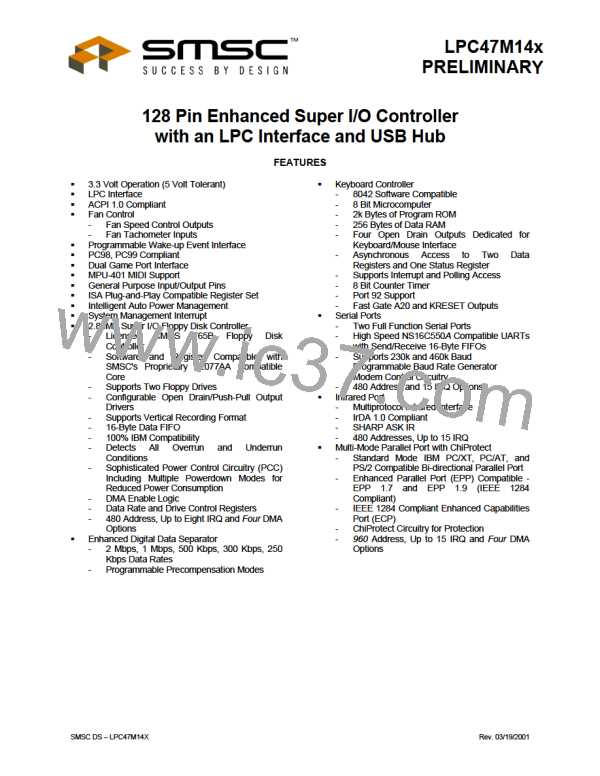

10 TIMING DIAGRAMS

For the Timing Diagrams shown, the following capacitive loads are used on outputs.

CAPACITANCE

TOTAL (pF)

NAME

SER_IRQ

LAD# [3:0]

LDRQ#

50

50

50

nDIR

nSTEP

240

240

nDS0

nDS1

240

240

PD[0:7]

nSTROBE

nALF

240

240

240

J1X-Y

J2X-Y

50

50

KDAT

240

KCLK

MDAT

240

240

MCLK

240

MIDI_Tx

FANx

50

50

LEDx

50

TXD1

TXD2

50

50

PD+[1:4] (Full-Speed)

PD-[1:4] (Full-Speed)

USB+ (Full-Speed)

USB− (Full-Speed)

PD+[1:4] (Low-Speed)

PD-[1:4] (Low-Speed)

USB+ (Low-Speed)

USB− (Low-Speed)

50

50

50

50

200-450 (Note 1)

200-450 (Note 1)

50-150

50-150

Note 1: Total capacitance of load with cable.

SMSC DS – LPC47M14X

Page 177

Rev. 03/19/2001

SMSC [ SMSC CORPORATION ]

SMSC [ SMSC CORPORATION ]