SX1232

WIRELESS & SENSING

DATASHEET

This product datasheet contains a detailed description of the SX1232 performance and functionality. Please consult the

Semtech website for the latest updates or errata.

1. General Description

The SX1232 is a single-chip integrated circuit ideally suited for today's high performance ISM band RF applications. The

SX1232's advanced feature set includes a state-of-the-art packet engine and top level sequencer. In conjunction with a 64

byte FIFO, these automate the entire process of packet transmission, reception and acknowledgement without incurring

the consumption penalty common to many transceivers that feature an on-chip MCU. Being easily configurable, it greatly

simplifies system design and reduces external MCU workload to an absolute minimum. The high level of integration

reduces the external BoM to passive decoupling and impedance matching components. It is intended for use as a high-

performance, low-cost FSK and OOK RF transceiver for robust, frequency agile, half-duplex, bi-directional RF links. Where

stable and constant RF performance is required over the full operating range of the device down to 1.8V the receiver and

PA are fully regulated. For transmit intensive applications - a high efficiency PA can be selected to optimize the current

consumption.

The SX1232 is intended for applications requiring high sensitivity and low receive current. Coupling the digital state

machine with an RF front end capable of delivering a link budget of 143dB (-123dBm sensitivity in conjunction with

+20dBm Pout). The SX1232 complies with both ETSI and FCC regulatory requirements and is available in a 5 x 5 mm QFN

24 lead package. The low-IF architecture of the SX1232 is well suited for low modulation index and narrow band operation.

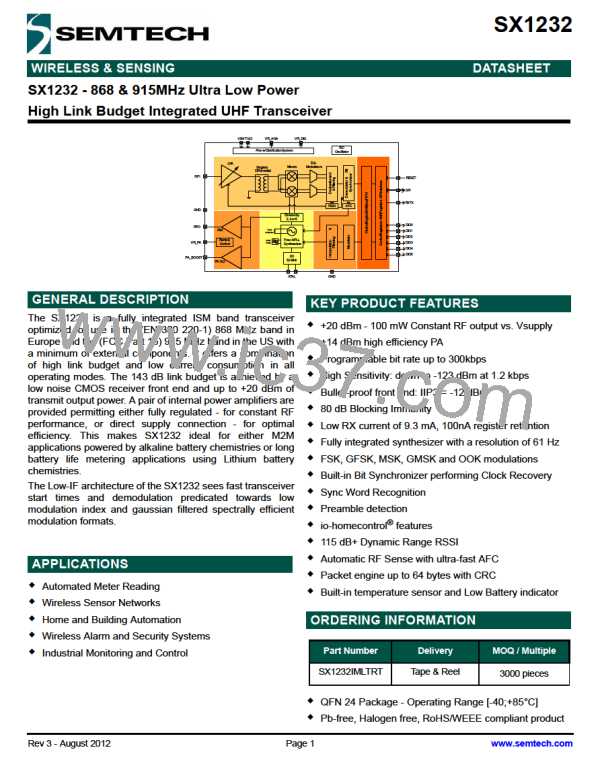

1.1. Simplified Block Diagram

VBAT1&2

VR_ANA

VR_DIG

RC

Oscillator

Pow erDistributionSystem

Σ/Δ

Modulators

LNA

Singleto

Mixers

Differential

RFI

RESET

SPI

RXTX

RSSI

AFC

GND

Divisionby

2,4 or6

DIO0

DIO1

DIO2

DIO3

DIO4

DIO5

RFO

VR_PA

Tank

Inductor

PA 0

Loop

Filter

Frac-NPLL

Synthesizer

Ramp&

Control

XO

32 MHz

PA_BOOST

PA 1&2

XTAL

GND

FrequencySynthesis

ReceiverBlocks

TransmitterBlocks

ControlBlocks

PrimarilyAnalog

Primarily Digital

Figure 1. Block Diagram

Rev 3 - August 2012

Page 9

www.semtech.com

SEMTECH [ SEMTECH CORPORATION ]

SEMTECH [ SEMTECH CORPORATION ]