SX1232

WIRELESS & SENSING

DATASHEET

List of Figures

Section

Page

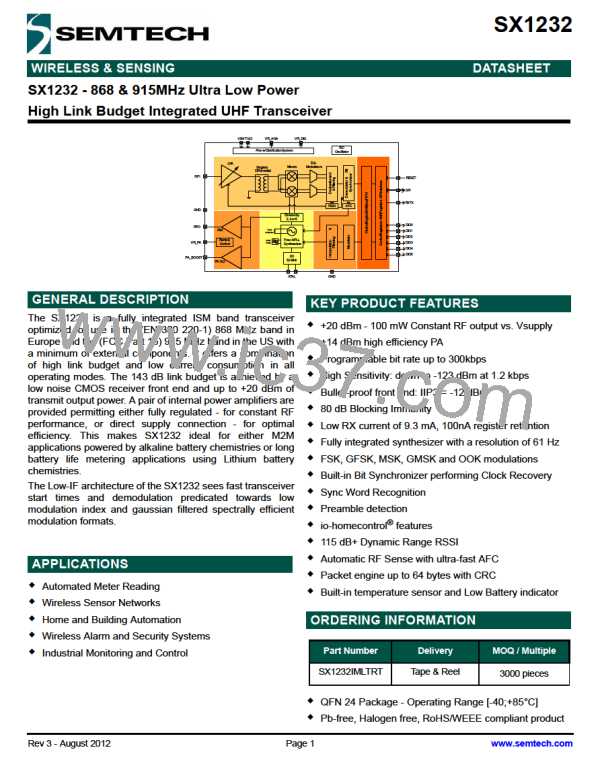

Figure 1. Block Diagram ................................................................................................................................................ 9

Figure 2. Pin Diagram .................................................................................................................................................. 10

Figure 3. Marking Diagram .......................................................................................................................................... 10

Figure 4. Simplified SX1232 Block Schematic Diagram .............................................................................................. 17

Figure 5. TCXO Connection ........................................................................................................................................ 19

Figure 6. Typical Phase Noise Performances of the Low Consumption and Low Phase Noise PLLs. ....................... 20

Figure 7. RF Front-end Architecture Shows the Internal PA Configuration. ............................................................... 22

Figure 8. Receiver Block Diagram ............................................................................................................................... 27

Figure 9. AGC Steps Definition ................................................................................................................................... 28

Figure 10. OOK Peak Demodulator Description .......................................................................................................... 30

Figure 11. Floor Threshold Optimization ..................................................................................................................... 31

Figure 12. Bit Synchronizer Description ...................................................................................................................... 33

Figure 13. FEI Process ................................................................................................................................................ 34

Figure 14. Temperature Sensor Response ................................................................................................................. 36

Figure 15. Startup Process .......................................................................................................................................... 38

Figure 16. Time to Rssi Sample .................................................................................................................................. 40

Figure 17. Tx to Rx Turnaround .................................................................................................................................. 40

Figure 18. Rx to Tx Turnaround .................................................................................................................................. 40

Figure 19. Receiver Hopping ....................................................................................................................................... 41

Figure 20. Transmitter Hopping ................................................................................................................................... 41

Figure 21. Timer1 and Timer2 Mechanism .................................................................................................................. 46

Figure 22. Sequencer State Machine .......................................................................................................................... 47

Figure 23. SX1232 Data Processing Conceptual View ............................................................................................... 48

Figure 24. SPI Timing Diagram (single access) .......................................................................................................... 49

Figure 25. FIFO and Shift Register (SR) ..................................................................................................................... 50

Figure 26. FifoLevel IRQ Source Behavior .................................................................................................................. 51

Figure 27. Sync Word Recognition .............................................................................................................................. 52

Figure 28. Continuous Mode Conceptual View ........................................................................................................... 54

Figure 29. Tx Processing in Continuous Mode ............................................................................................................ 54

Figure 30. Rx Processing in Continuous Mode ........................................................................................................... 55

Figure 31. Packet Mode Conceptual View ................................................................................................................... 56

Figure 32. Fixed Length Packet Format ...................................................................................................................... 57

Figure 33. Variable Length Packet Format .................................................................................................................. 58

Figure 34. Unlimited Length Packet Format ................................................................................................................ 58

Figure 35. Manchester Encoding/Decoding ................................................................................................................. 62

Figure 36. Data Whitening Polynomial ........................................................................................................................ 63

Figure 37. POR Timing Diagram ................................................................................................................................. 81

Figure 38. Manual Reset Timing Diagram ................................................................................................................... 82

Figure 39. Reference Design - Single RF Input/Output, High Efficiency PA ............................................................... 82

Rev 3 - August 2012

Page 5

www.semtech.com

SEMTECH [ SEMTECH CORPORATION ]

SEMTECH [ SEMTECH CORPORATION ]