SX1232

WIRELESS & SENSING

3. Chip Description

DATASHEET

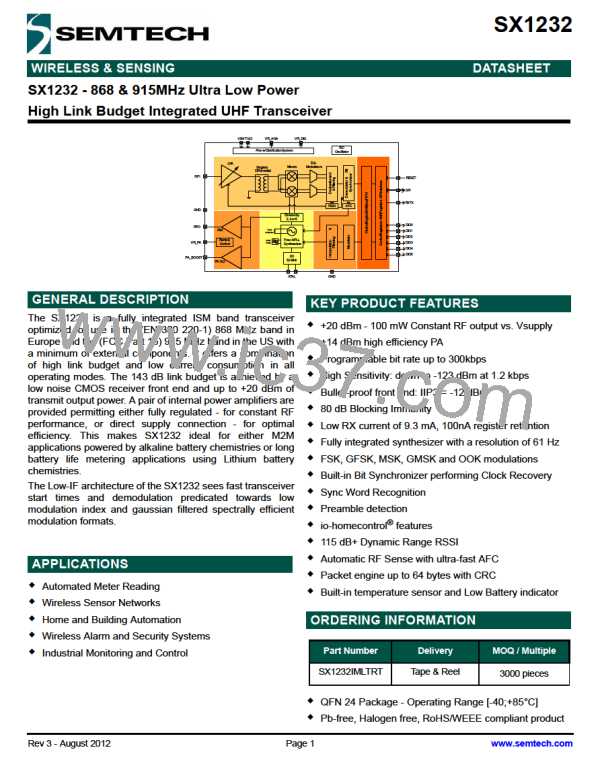

This section describes in depth the architecture of the SX1232 low-power, highly integrated transceiver. The following

figure shows a simplified block diagram of the SX1232.

Figure 4. Simplified SX1232 Block Schematic Diagram

SX1232 is a half-duplex, low-IF transceiver. Here the received RF signal is first amplified by the LNA. The LNA input is

single ended to minimise the external BoM and for ease of design. Following the LNA output, the conversion to differential

is made to improve the second order linearity and harmonic rejection. The signal is then down-converted to in-phase (I)

and quadrature (Q) components at the intermediate frequency (IF) by the mixer stage. A pair of sigma delta ADCs then

perform data conversion, with all subsequent signal processing and demodulation performed in the digital domain. The

digital state machine also controls the automatic frequency correction (AFC), received signal strength indicator (RSSI) and

automatic gain control (AGC). It also features the higher-level packet and protocol level functionality of the top level

sequencer.

In the receiver operating mode two states of functionality are defined. Upon initial transition to receiver operating mode the

receiver is in the ‘receiver-enabled’ state. In this state the receiver awaits for either the user defined valid preamble or RSSI

detection criterion to be fulfilled. Once met the receiver enters ‘receiver-active’ state. In this second state the received

signal is processed by the packet engine and top level sequencer.

The frequency synthesiser generates the local oscillator (LO) frequency for both receiver and transmitter. The PLL is

optimized for user-transparent low lock time and fast auto-calibrating operation. In transmission, frequency modulation is

performed digitally within the PLL bandwidth. It also features optional pre-filtering of the bit stream to improve spectral

purity.

Rev 3 - August 2012

Page 17

www.semtech.com

SEMTECH [ SEMTECH CORPORATION ]

SEMTECH [ SEMTECH CORPORATION ]