RT8876A

Operation

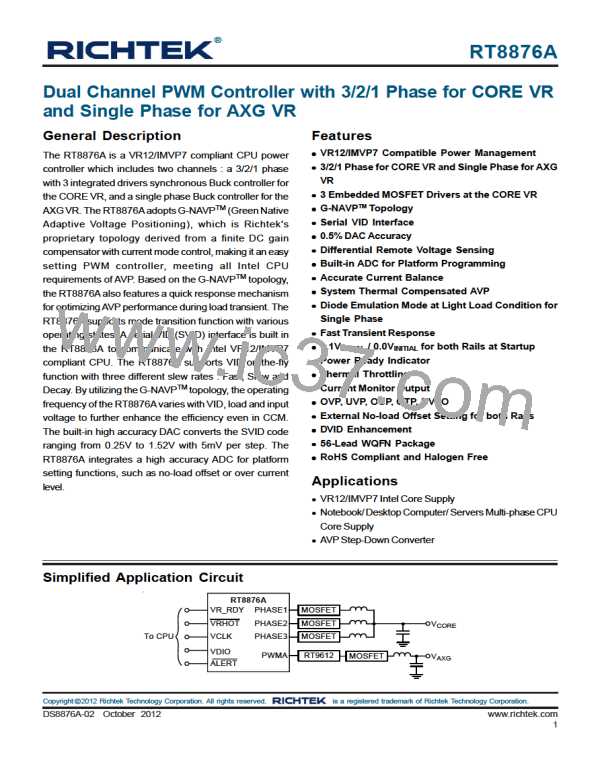

PWM CMP

Offset Cancellation

Generate a signal to trigger Ton pulse.

Cancel the current/voltage ripple issue to get the accurate

VSEN.

TON GEN

UVLO

Generate the PWM1 to PWM4 sequentially according

to the phase control signal from the Loop control

protection logic.

Detect theDVDand VCC voltage and issue POR signal as

they are large enough.

Control and Protection Logic

DAC

Execute the command from CPU.

Generate a analog signal according to the digital code

generated by Control Logic.

The control logic also generates the digital code of the

VID.

Soft-Start and Slew Rate Control

Control the Dynamic VID slew rate of VSET according to

the SetVID fast or SetVID slow.

Control the power on sequence

Control the protection behavior.

Control the operational phase number.

3-PHASE Driver

Generate UGATE [1:3] and LGATE [1:3] signal by PWM

[1:3] signal.

Current Balance

Generate the signal to control Ton to achieve current

balance.

Copyright 2012 Richtek Technology Corporation. All rights reserved.

©

is a registered trademark of Richtek Technology Corporation.

DS8876A-02 October 2012

www.richtek.com

5

RICHTEK [ RICHTEK TECHNOLOGY CORPORATION ]

RICHTEK [ RICHTEK TECHNOLOGY CORPORATION ]