RT8876A

Typical Application Circuit

VCCIO

RT8876A

48

VCC12

12V

41

VRHOT

VRHOT

35

17

VR_RDY

VCLK

VR_RDY

VCLK

36

VCC5

5V

18

19

VCC5

VDIO

VDIO

43

V

IN

TONSET

ALERT

ALERT

42

9

TONSETA

V

IN

14

21

22

23

32

1

OFS

TEMPMAX

ICCMAX

RSET

DVID

13

2

ICCMAXA

QRSETA

DVIDA

QRSET

OFSA

26

20

15

IBIAS

IMON

16

V

IMONFB

CC_SENSE

10

11

COMP

FB

25

37

38

IMONA

OCSETA

OCSET

R

NTC

V

IN

52

51

50

49

BOOT1

VCC5

VCC5

UGATE1

PHASE1

LGATE1

6

5

ISEN1P

ISEN1N

R

R

NTC

NTC

40

V

IN

TSEN

VCC5

VCC5

56

55

54

53

BOOT2

UGATE2

PHASE2

LGATE2

39

24

TSENA

V

OUT_CORE

3

4

ISEN2P

ISEN2N

IMONFBA

V

V

CCAXG_SENSE

IN

44

45

46

47

BOOT3

100

Load

UGATE3

PHASE3

LGATE3

29

28

COMPA

FBA

12V

R

NTC

12V

7

8

ISEN3P

ISEN3N

VCC

BOOT

UGATE

12

PGND

RGND

PHASE

LGATE

V

OUT_AXG

V

Chip Enable

33

SS_SENSE

34

PWMA

PWM

EN

100

Load

RT9612

31

30

ISENAP

ISENAN

RGNDA

27

57 (Exposed Pad)

V

GND

SSAXG_SENSE

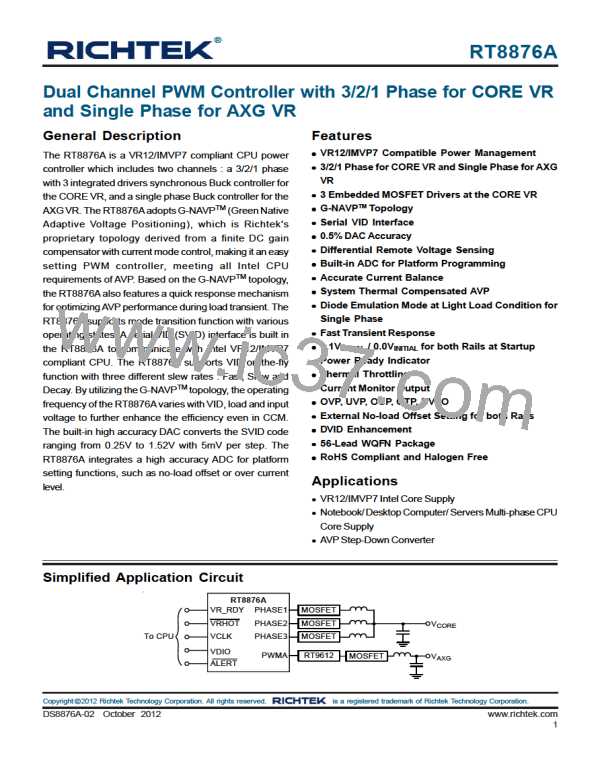

Figure 1. Thernal Compersation at Voltage Loop forAXGVR

Copyright 2012 Richtek Technology Corporation. All rights reserved.

©

is a registered trademark of Richtek Technology Corporation.

DS8876A-02 October 2012

www.richtek.com

21

RICHTEK [ RICHTEK TECHNOLOGY CORPORATION ]

RICHTEK [ RICHTEK TECHNOLOGY CORPORATION ]