4283 Group

LIST OF PRECAUTIONS

✕ Noise and latch-up prevention

Connect a capacitor on the following condition to prevent noise

and latch-up;

✕ Timer

•

Count source

Stop timer 1 or timer 2 counting to change its count source.

Reading the count value

•

•

connect a bypass capacitor (approx. 0.01 µF) between pins

VDD and VSS at the shortest distance,

equalize its wiring in width and length, and

use the thickest wire.

Port E2 is also uesd as VPP pin. Connect this pin to VSS

through the resistor about 5kΩ which is assigned to E2/VPP

pin as close as possible at the shortest distance.

Stop timer 1 or 2 counting and then execute the data read

instruction (TAB1, TAB2) to read its data.

Watchdog timer

Be sure that the timing to execute the WRST instruction in

order to operate WDT efficiently.

•

•

•

•

•

•

Writing to reload register R1

When writing data to reload register R1 while timer 1 is

operating, avoid a timing when timer 1 underflows.

Timer 1 count operation

✕ Register initial values 1

The initial value of the following registers are undefined after

system is released from reset. After system is released from

reset, set initial values.

• Register D (3 bits)

• Register E (8 bits)

When the bit 5 of the watchdog timer (WDT) is selected as

the timer 1 count source, the error of maximum ± 256 µs

(at the minimum instruction execution time : 8 µs) is

generated from timer 1 start until timer 1 underflow. When

programming, be careful about this error.

Stop of timer 2

•

•

✕ Register initial values 2

The initial value of the following registers are undefined at RAM

Avoid a timing when timer 2 underflows to stop timer 2.

Writing to reload register R2H

backup. After system is returned from RAM back-up, set initial

values.

• Register X (4 bits)

• Register Y (4 bits)

• Register D (3 bits)

• Register E (8 bits)

When writing data to reload register R2H while timer 2 is

operating, avoid a timing when timer underflows.

Timer 2 carrier wave output function

When to expand “H” interval of carrier wave is valid, set “1”

or more to reload register R2H.

•

•

Timer 1 and timer 2 carrier wave output function

Count starts from the rising edge in Fig. 29 after the first

✕

✕ Stack registers (SKS)

falling edge of the count source, after timer 1 and timer 2

Stack registers (SKs) are four identical registers, so that

subroutines can be nested up to 4 levels. However, one of

stack registers is used respectively when using an interrupt

service routine and when executing a table reference

instruction. Accordingly, be careful not to over the stack when

performing these operations together.

operations start in Fig. 29.

✕

Time to first underflow in Fig. 29 is different from time

✕

among next underflow in Fig. 29 by the timing to start the

✕

timer and count source operations after count starts.

✕

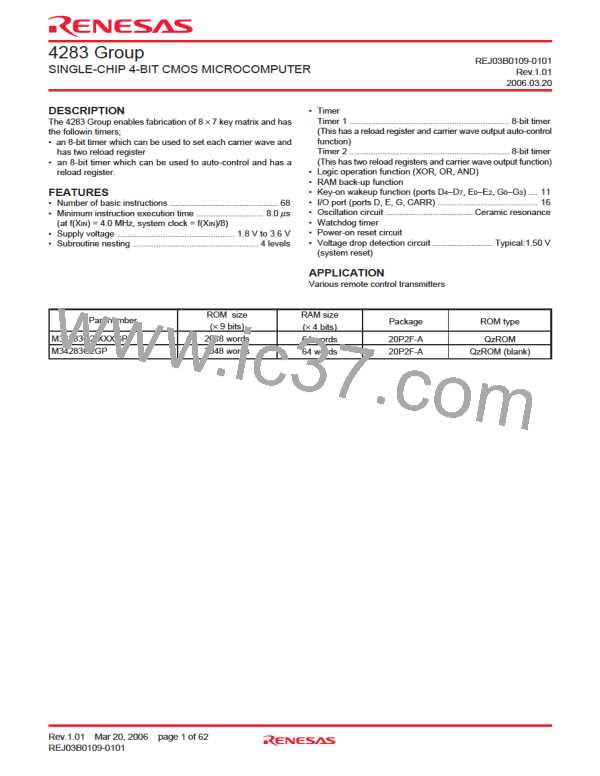

✕ Notes on unused pins

Count source

Connection

Pin

Usage condition

Timer value

3

2

1

0

3

2

1

0

3

Open.

D

D

0

–D

3

7

Connect to VDD.

Timer underflow signal

Open (Set the output latch to “1” ).

Open (Set the output latch to “0” ).

Connect to VDD.

4

–D

Pull-down transistor OFF.

✕

✕

Pull-down transistor OFF.

Pull-down transistor OFF.

✕

Timer start

Open (Set the output latch to “1” ).

Open (Set the output latch to “0” ).

Connect to VDD.

E

E

0

2

, E

1

Fig. 29 Count start time and count time when operation

starts (T1, T2)

Pull-down transistor OFF.

Open.

✕ Program counter

Connect to VSS.

Make sure that the program counter does not specify after the

last page of the built-in ROM.

Open (Set the output latch to “1” ).

Open (Set the output latch to “0” ).

Connect to VDD.

G

0

–G

3

Pull-down transistor OFF.

Pull-down transistor OFF.

Open.

CARR

(Note when connecting to VSS and VDD)

•

Connect the unused pins to VSS and VDD at the shortest

distance and use the thick wire against noise.

Rev.1.01 Mar 20, 2006 page 23 of 62

REJ03B0109-0101

RENESAS [ RENESAS TECHNOLOGY CORP ]

RENESAS [ RENESAS TECHNOLOGY CORP ]