FM25W256 - 256Kb SPI F-RAM

CS

0

1

2

3

4

5

6

7

0

1

2

3

4

6

7

0

1

6

2

5

3

4

3

5

2

6

1

7

7

SCK

16-bit Address

12 11

Data In

4

Op-code

SI

0

0

0

1

0

X

14

13

1

0

7

0

0

0

0

0

MSB

LSB MSB

LSB

Hi-Z

SO

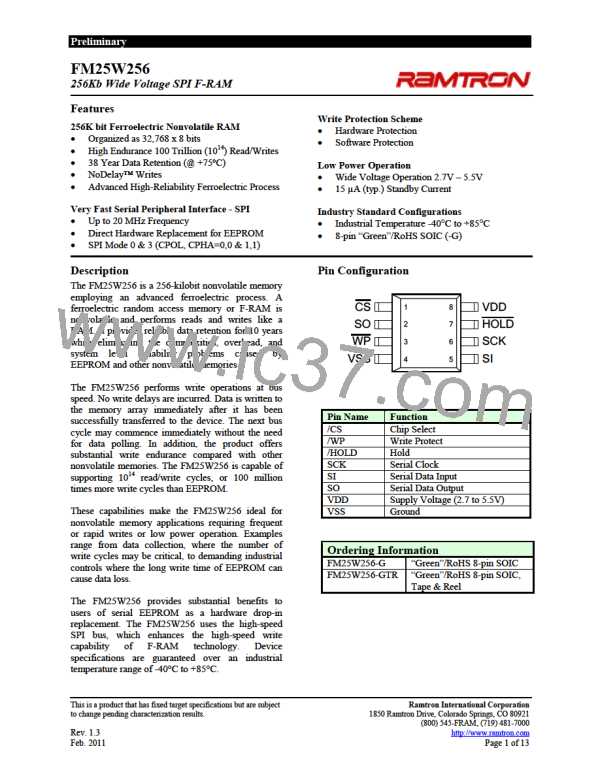

Figure 9. Memory Write

(WREN must precede WRITE)

CS

0

1

2

3

4

5

6

7

0

1

2

3

4

6

7

0

1

6

2

5

3

4

3

5

2

6

1

7

7

SCK

16-bit Address

12 11

Op-code

0

SI

0

0

0

1

1

X

14

13

1

0

0

0

MSB

LSB

Data Out

4

Hi-Z

SO

7

0

0

MSB

LSB

Figure 10. Memory Read

64-bits each. The entire row is internally accessed

once whether a single byte or all eight bytes are read

or written. Each byte in the row is counted only once

in an endurance calculation. The table below shows

endurance calculations for 64-byte repeating loop,

which includes an op-code, a starting address, and a

sequential 64-byte data stream. This causes each byte

to experience one endurance cycle through the loop.

F-RAM read and write endurance is virtually

unlimited even at 20MHz clock rate.

Endurance

The FM25W256 device is capable of operating at

least 1014 read or write cycles. A F-RAM memory

operates with

a read and restore mechanism.

Therefore, an endurance cycle is applied on a row

basis for each access (read or write) to the memory

array. The F-RAM architecture is based on an array

of rows and columns. Rows are defined by A14-A3

and column addresses by A2-A0.

See Block

Diagram (pg 2) which shows the array as 4K rows of

Table 5. Time to Reach Endurance Limit for Repeating 64-byte Loop

SCK Freq Endurance Endurance Years to Reach

(MHz) Cycles/sec.

1014 Cycles

Cycles/year

20

10

5

37,310

18,660

9,330

1.18 x 1012

5.88 x 1011

2.94 x 1011

85.1

170.2

340.3

Rev. 1.3

Feb. 2011

Page 8 of 13

RAMTRON [ RAMTRON INTERNATIONAL CORPORATION ]

RAMTRON [ RAMTRON INTERNATIONAL CORPORATION ]