(Preliminary)PL611s-19

0.5kHz-55MHz MHz to KHz Programmable ClockTM

FUNCTIONAL DESCRIPTION

PL611s-19 is a highly featured, very flexible, advanced programmable PLL design for high performance, low-

power, small form-factor applications. The PL611s-19 accepts a reference clock input of 1MHz to 200MHz and is

capable of producing two outputs up to 125MHz. This flexible design allows the PL611s-19 to deliver any PLL

generated frequency, FREF (Ref Clk) frequency or FREF /(2*P) to CLK0 and/or CLK1. Some of the design features

of the PL611s-19 are mentioned below:

PLL Programming

Programmable I/O (OE/PDB/FSEL)

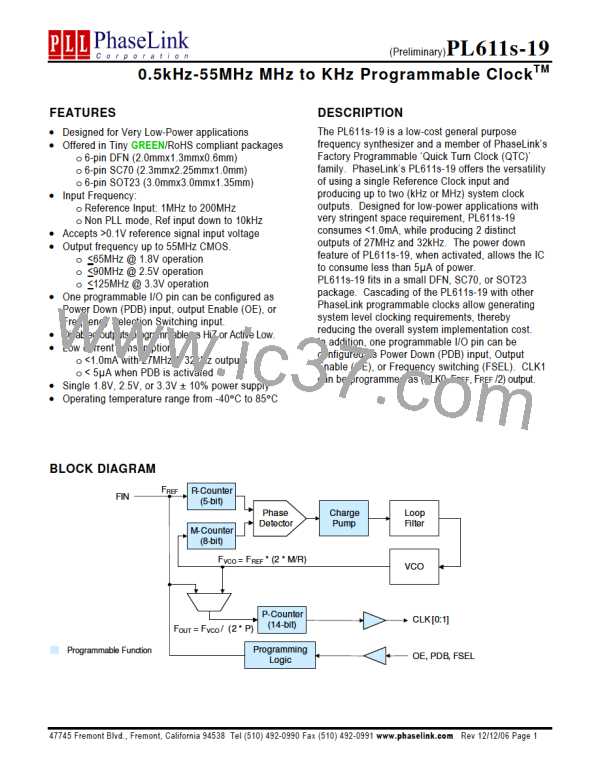

The PLL in the PL611s-19 is fully programmable.

The PLL is equipped with an 5-bit input frequency

divider (R-Counter), and an 8-bit VCO frequency

feedback loop divider (M-Counter). The output of

the PLL is transferred to a 14-bit post VCO divider

(P-Counter). The output frequency is determined by

the following formula [FOUT = FREF * M / (R * P) ].

The PL611s-19 provides one programmable I/O pin

which can be configured as one of the following

functions:

Output Enable (OE)

The Output Enable feature allows the user to enable

and disable CLK0 clock output by toggling the OE

pin. CLK1 remains active when OE is pulled low.

The OE pin incorporates a 60kΩ pull up resistor

giving a default condition of logic “1”.

Clock Output (CLK0)

The output of CLK0 can be configured as the PLL output

(FVCO/(2*P)), FREF (Ref Clk Frequency) output, or

The OE feature can be programmed to allow the

output to float (Hi Z), or to operate in the ‘Active low’

mode.

F

REF/(2*P) output. The output drive level can be

programmed to Low Drive (4mA), Standard Drive

(8mA) or High Drive (16mA). The maximum output

frequency is 125MHz.

Power-Down Control (PDB)

The Power Down (PDB) feature allows the user to put

the PL611s-19 into “Sleep Mode”. When activated

(logic ‘0’), PDB ‘Disables the PLL, the oscillator

circuitry, counters, and all other active circuitry. In

Power Down mode the IC consumes <5µA of power.

The PDB pin incorporates a 60kΩ pull up resistor

giving a default condition of logic “1”.

Clock Output (CLK1)

The output of CLK1 can be configured as:

F

F

REF - Reference ( Ref Clk ) Frequency

REF / 2

CLK0

CLK0 / 2

When using the OE function CLK1 will remain

“Always On” and will not be disabled when OE is

pulled low. When using the PDB function CLK1 will

be disabled along with CLK0. The output drive level

can be programmed to Low Drive (4mA), Standard

Drive (8mA) or High Drive (16mA). The maximum

output frequency is 125MHz.

The PDB feature can be programmed to allow the

output to float (Hi Z), or to operate in the ‘Active low’

mode.

Frequency Select (FSEL)

The Frequency Select (FSEL) feature allows the

PL611s-19 to switch between two pre-programmed

outputs allowing the device “On the Fly” frequency

switching. The FSEL pin incorporates a 60kΩ pull up

resistor giving a default condition of logic “1”.

47745 Fremont Blvd., Fremont, California 94538 Tel (510) 492-0990 Fax (510) 492-0991 www.phaselink.com Rev 12/12/06 Page 3

PLL [ PHASELINK CORPORATION ]

PLL [ PHASELINK CORPORATION ]