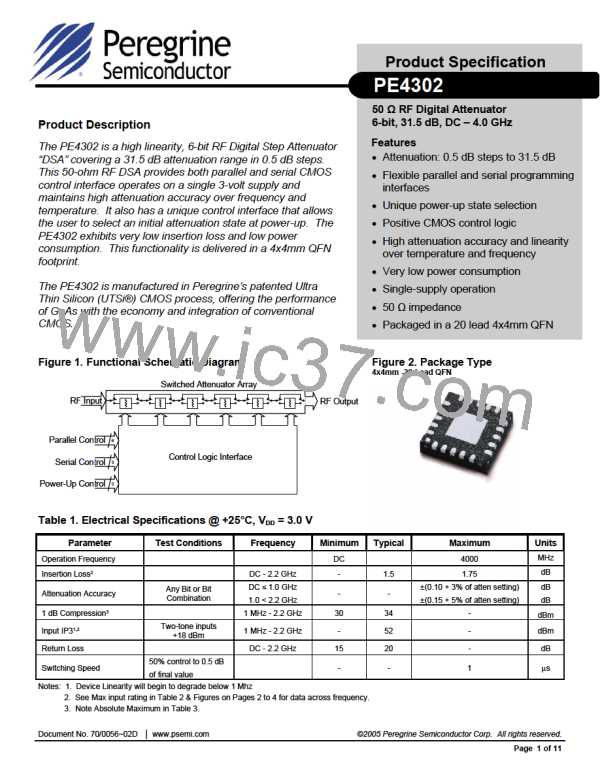

PE4302

Product Specification

Programming Options

Clock, and Latch Enable (LE). The Data and Clock

inputs allow data to be serially entered into the shift

register, a process that is independent of the state of

the LE input.

Parallel/Serial Selection

Either a parallel or serial interface can be used to

control the PE4302. The P/S bit provides this

selection, with P/S=LOW selecting the parallel

interface and P/S=HIGH selecting the serial

interface.

The LE input controls the latch. When LE is HIGH,

the latch is transparent and the contents of the serial

shift register control the attenuator. When LE is

brought LOW, data in the shift register is latched.

Parallel Mode Interface

The parallel interface consists of five CMOS-

compatible control lines that select the desired

attenuation state, as shown in Table 5.

The shift register should be loaded while LE is held

LOW to prevent the attenuator value from changing

as data is entered. The LE input should then be

toggled HIGH and brought LOW again, latching the

new data. The timing for this operation is defined by

Figure 17 (Serial Interface Timing Diagram) and

Table 8 (Serial Interface AC Characteristics).

The parallel interface timing requirements are

defined by Figure 18 (Parallel Interface Timing

Diagram), Table 9 (Parallel Interface AC

Characteristics), and switching speed (Table 1).

Power-up Control Settings

For latched parallel programming the Latch Enable

(LE) should be held LOW while changing attenuation

state control values, then pulse LE HIGH to LOW

(per Figure 18) to latch new attenuation state into

device.

The PE4302 always assumes a specifiable

attenuation setting on power-up. This feature exists

for both the Serial and Parallel modes of operation,

and allows a known attenuation state to be

established before an initial serial or parallel control

word is provided.

For direct parallel programming, the Latch Enable

(LE) line should be pulled HIGH. Changing

attenuation state control values will change device

state to new attenuation. Direct Mode is ideal for

manual control of the device (using hardwire,

switches, or jumpers).

When the attenuator powers up in Serial mode (P/

S=1), the six control bits are set to whatever data is

present on the six parallel data inputs (C0.5 to C16).

This allows any one of the 64 attenuation settings to

be specified as the power-up state.

Table 5. Truth Table

When the attenuator powers up in Parallel mode (P/

S=0) with LE=0, the control bits are automatically set

to one of four possible values. These four values

are selected by the two power-up control bits, PUP1

and PUP2, as shown in Table 6 (Power-Up Truth

Table, Parallel Mode).

Attenuation

P/S C16 C8

C4

C2

C1 C0.5

State

Reference Loss

0.5 dB

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

0

0

0

0

0

1

0

1

0

0

0

0

1

0

0

1

0

0

0

1

0

0

0

1

0

0

1

0

0

0

0

1

0

1

0

0

0

0

0

1

1 dB

2 dB

Table 6. Parallel PUP Truth Table

4 dB

8 dB

P/S

0

LE

0

PUP2 PUP1

Attenuation State

Reference Loss

8 dB

16 dB

31.5 dB

0

1

0

1

X

0

0

1

1

X

0

0

Note: Not all 64 possible combinations of C0.5-C16 are shown in table

0

0

16 dB

0

0

31 dB

Serial Interface

0

1

Defined by C0.5-C16

The serial interface is a 6-bit serial-in, parallel-out

shift register buffered by a transparent latch. It is

controlled by three CMOS-compatible signals: Data,

Note: Power up with LE=1 provides normal parallel operation with

C0.5-C16, and PUP1 and PUP2 are not active.

©2005 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70/0056~02D │ UltraCMOS™ RFIC Solutions

Page 6 of 11

PSEMI [ Peregrine Semiconductor ]

PSEMI [ Peregrine Semiconductor ]