NCP1239

FB<Vpin1 => Skip high

+

Skip

HV

16

−

Stby_detect

FB

100k

S

R

Skip

adjust

7

UVLOs

Latch

Reset

Q

Q

+

15r

450mV

+

−

25r

Internal

Thermal

Shutdown

FB>1.6*Vpin1 =>Stby_detect RESET

−

15

14

UVLO

TSD

(Vcc<VccOFF)

Fault

detect

3

OVL

+

2.5V

S

regOUT

Fault

Q

Q

Vcc

R

Vdd

Regul

Vcc < 4V

10k

PFC_Vcc

1

stdwn

pfcON

pfcOFF

1mA

13

Vcc

Stby

Startup Phase

OVL

Vstop

S

R

Q

Q

Vdd

Vdd

Divider by 2

Vcc<7V

Stby_detect

Error_Flag

Soft−Start

and timer

management

6

2

SS / timer

Output

Buffer

OUTon

Drv

12

Soft−Start

Ipk limit

Jittering

Modulation

14V

clamp

REF5V

+

5V

Ramp

Compensation

pfcON

3.2V

32k

11

GND

CLK

BO_in

BO

−

+

5

BO_out

S

Q

+

Q

R

0.5V / 0.25V

Vdd

10

LEB

CS

Vstop

Vdd

BO_in

Oscillator

75 mA/V x V

pin5

CLK

4

−

+

Rt

9

Over Power

Limit

2.5V

Skip

Jittering

Modulation

LEB

+

−

“Jittered”

Reference

Vdd

+

+

−

0.5V

20k

FB

8

/ 3

0.9V

Error flag

to Skip

Soft−Start

Ipk limit

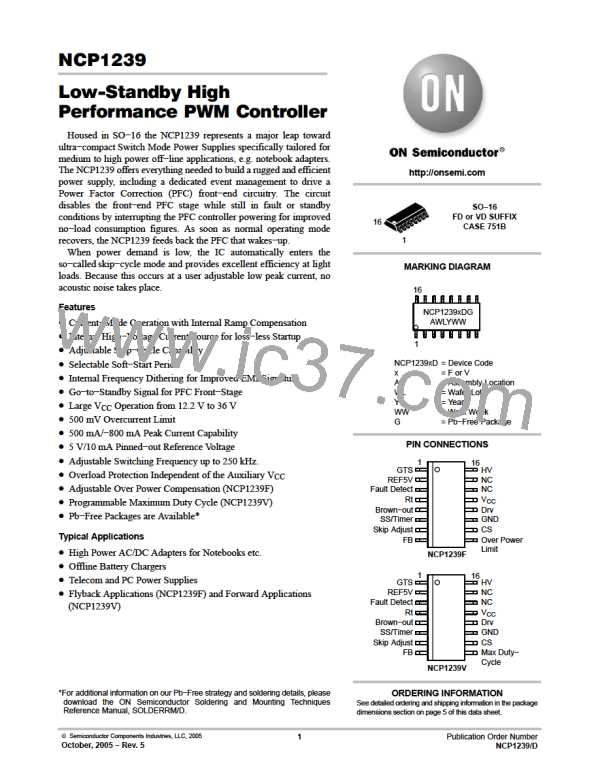

Figure 3. NCP1239F Internal Circuit Architecture

http://onsemi.com

7

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]