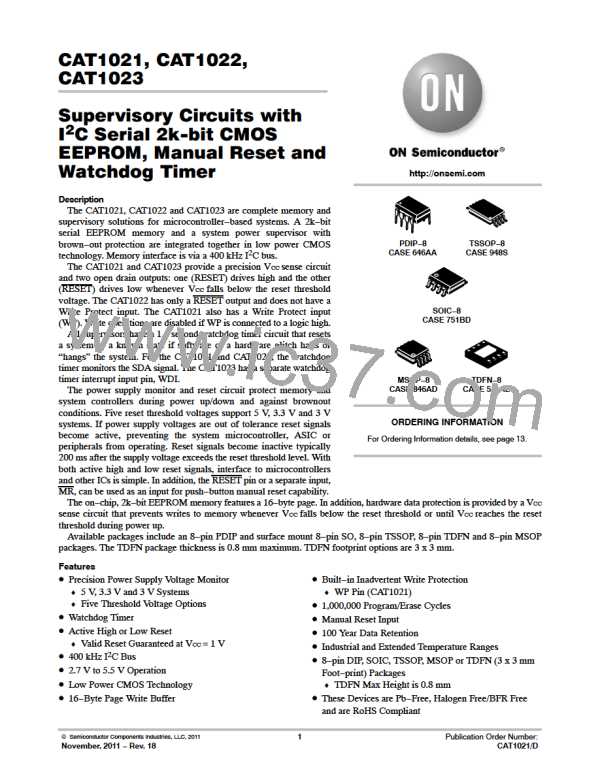

CAT1021, CAT1022, CAT1023

S

T

A

R

T

S

T

O

P

BUS ꢀACTIVITꢀY:

MASTER

SLꢀAVE

ADDRESS

SDꢀA LINE

S

P

A

C

K

N

O

DATA

A

C

K

SCꢀL

8

9

SDꢀAꢂꢂꢂꢂꢂꢂꢂꢂꢂꢂꢂꢂꢂ8TH BIꢀT

DATA OUꢀT

NO ACK

STOP

Figure 10. Immediate Address Read Timing

Immediate/Current Address Read

sends the START condition and the slave address again, this

time with the R/W bit set to one. The CAT1021/22/23 then

responds with its acknowledge and sends the 8−bit byte

requested. The master device does not send an acknowledge

but will generate a STOP condition.

The CAT1021/22/23 address counter contains the address

of the last byte accessed, incremented by one. In other

words, if the last READ or WRITE access was to address N,

the READ immediately following would access data from

address N + 1. For N = E = 255, the counter will wrap around

to zero and continue to clock out valid data. After the

CAT1021/22/23 receives its slave address information (with

the R/W bit set to one), it issues an acknowledge, then

transmits the 8−bit byte requested. The master device does

not send an acknowledge, but will generate a STOP

condition.

Sequential Read

The Sequential READ operation can be initiated by either

the Immediate Address READ or Selective READ

operations. After the CAT1021/22/23 sends the inital 8− bit

byte requested, the Master will responds with an

acknowledge which tells the device it requires more data.

The CAT1021/22/23 will continue to output an 8− bit byte

for each acknowledge, thus sending the STOP condition.

The data being transmitted from the CAT1021/22/23 is

sent sequentially with the data from address N followed by

data from address N + 1. The READ operation address

counter increments all of the CAT1021/22/23 address bits so

that the entire memory array can be read during one

operation.

Selective/Random Read

Selective/Random READ operations allow the Master

device to select at random any memory location for a READ

operation. The Master device first performs a ‘dummy’

write operation by sending the START condition, slave

address and byte addresses of the location it wishes to read.

After the CAT1021/22/23 acknowledges, the Master device

S

T

A

R

T

S

T

A

R

T

S

T

O

P

BUS ACTIVITY:

MASTER

SLAVE

ADDRESS

BYTE

ADDRESS (n)

SLAVE

ADDRESS

SDA LINE

S

S

P

A

C

K

A

C

K

A

C

K

N

O

DATA n

A

C

K

Figure 11. Selective Read Timing

http://onsemi.com

12

ONSEMI [ ONSEMI ]

ONSEMI [ ONSEMI ]