NXP Semiconductors

FXTH87E

FXTH87E, Family of Tire Pressure Monitor Sensors

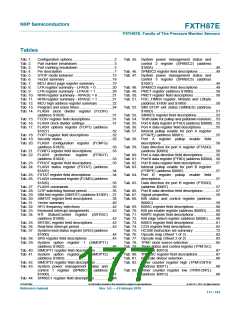

13.3

PWU control/status register 0 — PWUCS0

15.5.2

15.5.3

15.6

15.6.1

15.6.2

15.6.3

15.6.4

15.6.5

Bi-Phase encoding .........................................140

NRZ encoding ................................................141

RF output stage .............................................143

Modulation method ........................................ 143

Carrier frequency ...........................................143

RF power output ............................................143

Transmission error .........................................144

(address $0039) ............................................ 108

PWU control/status register 1 — PWUCS1 ....110

PWU wakeup status register — PWUS ......... 110

Functional modes .......................................... 111

RUN mode .....................................................111

STOP4 mode .................................................111

STOP1 mode .................................................111

Active BDM/foreground commands ............... 112

LF Receiver ......................................................112

Features .........................................................113

Modes of operation ........................................114

Power management .......................................114

Input amplifier ................................................ 114

LFR data mode states ...................................115

Carrier detect .................................................115

Auto-zero sequence .......................................117

Data recovery ................................................ 117

Data clock recovery and synchronization .......117

Manchester decode ....................................... 118

Duty-cycle for data mode .............................. 118

Input signal envelope .....................................119

Telegram verification ..................................... 120

Error detection and handling ......................... 121

Continuous ON mode ....................................121

Initialization information ................................. 121

LFR register definition ................................... 122

13.4

13.5

13.6

13.6.1

13.6.2

13.6.3

13.6.4

14

14.1

14.2

14.3

14.4

14.5

14.6

14.7

14.8

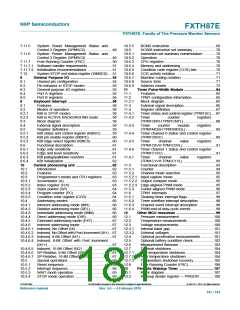

Supply

voltage

check

during

RF

transmission ...................................................144

RF Reset (RFMRST) .....................................144

RF interrupt ....................................................144

Datagram transmission times ........................ 144

RFM registers ................................................ 145

RFM Control Register 0 — RFCR0 ............... 145

RFM control register 1 — RFCR1 ................. 145

RFM control register 2 — RFCR2 ................. 146

15.6.6

15.7

15.8

15.9

15.9.1

15.10

15.11

15.11.1 Power working domains ................................ 147

15.11.1.1 PTYP ..............................................................147

15.11.1.2 PMIN ..............................................................147

15.12

15.13

15.14

15.15

15.16

15.17

14.9

14.10

14.11

14.12

14.13

14.14

14.15

14.16

14.17

RFM control register 3 — RFCR3 ................. 148

RFM control register 4 — RFCR4 ................. 149

RFM control register 5 — RFCR5 ................. 149

RFM control register 6 — RFCR6 ................. 150

RFM control register 7 — RFCR7 ................. 150

PLL control registers

RPAGE = 0 ....................................................152

PLL control registers PLLCR[3:2],

A - PLLCR[1:0],

15.18

B -

14.17.1 LF control register 1 (LFCTL1) ...................... 122

14.17.2 LF control register 2 (LFCTL2) ...................... 123

14.17.3 LF control register 3 (LFCTL3) ...................... 124

14.17.4 LFR control register 4 (LFCTL4) ....................126

14.17.5 LFR status register (LFS, LPAGE = 0) .......... 127

14.17.6 LFR data register (LFDATA, LPAGE = 0) ...... 128

14.17.7 LFR ID registers (LFIDH:LFIDL, LPAGE = 0) ..129

14.17.7.1 LF Control E — LFCTRLE .............................129

14.17.8 LFR control register D (LFCTRLD, LPAGE =

1) ....................................................................130

RPAGE = 0 ....................................................153

EPR register — EPR (RPAGE = 1) ............... 154

RF DATA registers — RFD[31:0] ...................154

VCO calibration machine ...............................155

Firmware .......................................................... 156

Software jump table .......................................156

Function documentation ................................ 156

General rules .................................................157

15.19

15.20

15.21

16

16.1

16.2

16.2.1

16.2.1.1 FXTH87E single Z-axis firmware routines ......157

16.2.1.2 FXTH87E dual XZ-axis firmware routines ......158

14.17.9 LFR control register C (LFCTRLC, LPAGE =

1) ....................................................................131

14.17.10 LFR control register B (LFCTRLB, LPAGE =

1) ....................................................................132

14.17.11 LFR control register A (LFCTRLA, LPAGE =

1) ....................................................................132

16.2.2

16.2.3

16.3

16.3.1

17

17.1

17.1.1

17.2

Device identification .......................................160

Definition of signal ranges ............................. 161

Memory resource usage ................................163

Software stack ............................................... 163

Development support ..................................... 163

Introduction .................................................... 163

Features .........................................................163

Background debug controller (BDC) ..............163

BKGD/PTA4 pin description .......................... 164

Communication details .................................. 165

BDC commands .............................................167

15

15.1

RF module ....................................................... 133

RF data modes ..............................................134

RF data buffer mode ..................................... 134

MCU direct mode .......................................... 135

RF output buffer data frame .......................... 135

Data buffer length ..........................................136

End of Message (EOM) .................................136

Transmission randomization ..........................136

Initial time interval ..........................................137

Interframe time intervals ................................ 138

Base time interval ..........................................138

Pseudo-random time interval .........................138

Frame number time ....................................... 139

RFM in STOP1 mode ....................................140

Data encoding ............................................... 140

Manchester encoding .................................... 140

15.1.1

15.1.2

15.2

15.2.1

15.2.2

15.3

15.3.1

15.3.2

15.3.3

15.3.4

15.3.5

15.4

17.2.1

17.2.2

17.2.3

17.2.3.1 Coding structure nomenclature ......................167

17.2.4

17.3

17.3.1

17.3.2

17.3.3

17.3.4

BDC hardware breakpoint ............................. 169

Register definition ..........................................169

BDC registers and control bits .......................169

BDC status and control register (BDCSCR) ... 170

BDC breakpoint match register (BDCBKPT) .. 171

System background debug force reset

register (SBDFR) ........................................... 171

Battery charge consumption modeling .........172

Standby current ............................................. 172

Measurement events ..................................... 172

18

18.1

18.2

15.5

15.5.1

FXTH87ERM

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2019. All rights reserved.

Reference manual

Rev. 5.0 — 4 February 2019

182 / 183

NXP [ NXP ]

NXP [ NXP ]