NXP Semiconductors

FXTH87E

FXTH87E, Family of Tire Pressure Monitor Sensors

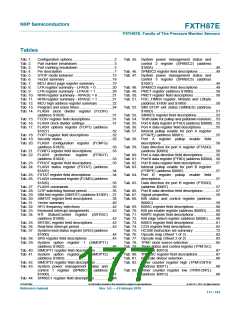

7.11.5

7.11.6

7.11.7

System Power Management Status and

10.5.5

10.6

BGND instruction .............................................69

HCS08 instruction set summary ...................... 70

Instruction set summary nomenclature ............70

Operators .........................................................70

CPU registers .................................................. 70

Memory and addressing ..................................70

Condition code register (CCR) bits ..................70

CCR activity notation .......................................71

Machine coding notation ..................................71

Source form .....................................................71

Address modes ................................................72

Timer Pulse-Width Module ...............................84

Features ...........................................................85

TPM1 configuration information .......................85

Block diagram ..................................................85

External signal description ...............................86

Register definition ............................................87

Timer status and control register (TPM1SC) ....87

Control 2 Register (SPMSC2) ......................... 48

System Power Management Status and

Control 3 Register (SPMSC3) ......................... 49

Free-Running Counter (FRC) .......................... 50

10.6.1

10.6.2

10.6.3

10.6.4

10.6.5

10.6.6

10.6.7

10.6.8

10.6.9

11

11.1

11.2

11.2.1

11.3

11.4

7.11.7.1 Software handler requirements ........................51

7.11.7.2 Initialization recommendations .........................51

7.12

8

8.1

8.2

8.3

8.4

8.5

9

9.1

9.2

9.2.1

9.2.2

9.3

System STOP exit status register (SIMSES) ....51

General Purpose I/O ......................................... 52

Unused pin configuration .................................54

Pin behavior in STOP modes ..........................55

General purpose I/O registers ......................... 55

Port A registers ................................................55

Port B registers ................................................56

Keyboard Interrupt ............................................58

Features ...........................................................58

Modes of operation ..........................................58

KBI in STOP modes ........................................58

KBI in ACTIVE BACKGROUND mode .............58

Block diagram ..................................................58

External signal description ...............................59

Register definitions .......................................... 59

KBI status and control register (KBISC) ...........59

KBI pin enable register (KBIPE) ...................... 60

KBI edge select register (KBIES) .................... 60

Functional description ......................................61

Edge only sensitivity ........................................61

Edge and level sensitivity ................................61

KBI pullup/pulldown resistors ...........................61

KBI initialization ............................................... 62

Central processing unit ....................................62

Introduction ...................................................... 62

Features ...........................................................62

Programmer’s model and CPU registers ......... 63

Accumulator (A) ...............................................63

Index register (H:X) ......................................... 63

Stack pointer (SP) ........................................... 64

Program counter (PC) ..................................... 64

Condition code register (CCR) ........................ 64

Addressing modes ...........................................66

Inherent addressing mode (INH) ..................... 66

Relative addressing mode (REL) .....................66

Immediate addressing mode (IMM) ................. 66

Direct addressing mode (DIR) .........................66

Extended addressing mode (EXT) ...................67

Indexed addressing mode ............................... 67

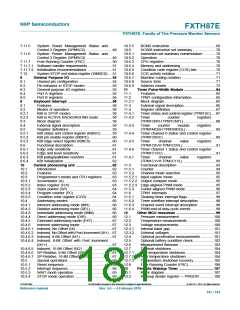

11.4.1

11.4.2

Timer

(TPM1CNTH:TPM1CNTL) ............................... 88

Timer counter modulo registers

counter

registers

9.4

9.5

11.4.3

11.4.4

11.4.5

11.4.6

11.4.7

(TPM1MODH:TPM1MODL) ............................. 89

Timer channel 0 status and control register

(TPM1C0SC) ................................................... 89

9.5.1

9.5.2

9.5.3

9.6

9.6.1

9.6.2

9.6.3

9.6.4

10

10.1

10.2

10.3

10.3.1

10.3.2

10.3.3

10.3.4

10.3.5

10.4

10.4.1

10.4.2

10.4.3

10.4.4

10.4.5

10.4.6

Timer

channel

value

registers

(TPM1C0VH:TPM1C0VL) ................................91

Timer channel 1 status and control register

(TPM1C1SC) ................................................... 91

Timer

channel

value

registers

(TPM1C1VH:TPM1C1VL) ................................93

Functional description ......................................93

Counter ............................................................ 94

Channel mode selection ..................................95

11.5

11.5.1

11.5.2

11.5.2.1 Input capture mode ......................................... 95

11.5.2.2 Output compare mode .....................................95

11.5.2.3 Edge-aligned PWM mode ................................95

11.5.3

11.6

11.6.1

11.6.2

11.6.3

11.6.4

12

12.1

12.2

12.3

12.3.1

12.3.2

12.4

12.5

12.6

Center-aligned PWM mode ............................. 96

TPM1 interrupts ............................................... 97

Clearing timer interrupt flags ........................... 98

Timer overflow interrupt description .................98

Channel event interrupt description .................98

PWM end-of-duty-cycle events ........................98

Other MCU resources .......................................99

Pressure measurement ................................. 100

Temperature measurements ..........................100

Voltage measurements ..................................100

Internal band gap .......................................... 101

External voltages ........................................... 101

Optional acceleration measurements ............ 101

Optional battery condition check ....................102

Measurement firmware ..................................103

Thermal shutdown ......................................... 104

Low temperature shutdown ........................... 104

High temperature shutdown ...........................104

Temperature shutdown recovery ................... 105

Free-Running Counter (FRC) ........................ 106

Periodic Wakeup Timer .................................. 107

Block diagram ................................................107

Wakeup divider register — PWUDIV ............. 108

10.4.6.1 Indexed, No Offset (IX) ....................................67

10.4.6.2 Indexed, No Offset with Post Increment (IX+) ...67

10.4.6.3 Indexed, 8-Bit Offset (IX1) ...............................67

10.4.6.4 Indexed, 8-Bit Offset with Post Increment

(IX1+) ...............................................................67

10.4.6.5 Indexed, 16-Bit Offset (IX2) .............................67

10.4.6.6 SP-Relative, 8-Bit Offset (SP1) ........................67

10.4.6.7 SP-Relative, 16-Bit Offset (SP2) ......................67

12.7

12.7.1

12.7.2

12.7.3

12.8

13

13.1

10.5

Special operations ........................................... 68

Reset sequence ...............................................68

Interrupt sequence ...........................................68

WAIT mode operation ......................................69

STOP mode operation .....................................69

10.5.1

10.5.2

10.5.3

10.5.4

13.2

FXTH87ERM

All information provided in this document is subject to legal disclaimers.

© NXP B.V. 2019. All rights reserved.

Reference manual

Rev. 5.0 — 4 February 2019

181 / 183

NXP [ NXP ]

NXP [ NXP ]