Nexperia

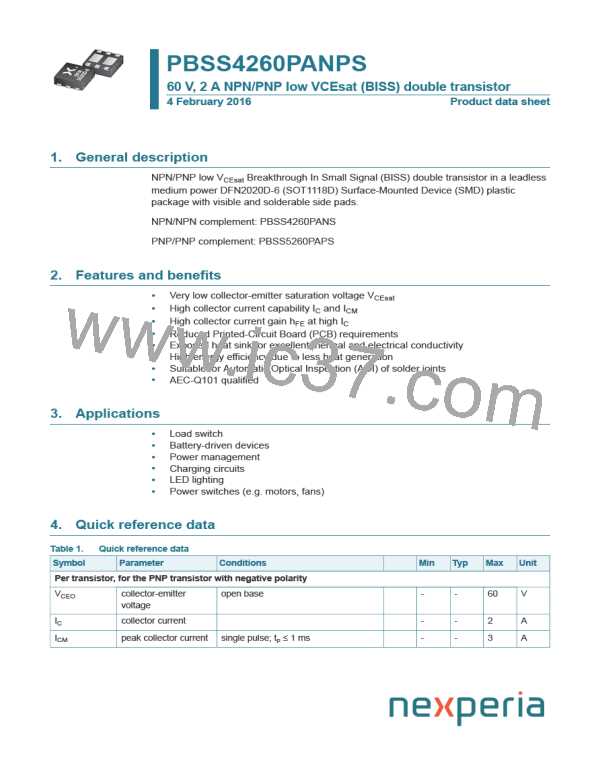

PBSS4260PANPS

60 V, 2 A NPN/PNP low VCEsat (BISS) double transistor

16. Contents

1

2

3

4

5

6

7

8

9

10

General description ............................................... 1

Features and benefits ............................................1

Applications ........................................................... 1

Quick reference data ............................................. 1

Pinning information ...............................................2

Ordering information .............................................2

Marking ...................................................................2

Limiting values .......................................................3

Thermal characteristics .........................................4

Characteristics .......................................................7

11

Test information ...................................................14

11.1

Quality information ............................................. 15

12

13

14

Package outline ................................................... 16

Soldering .............................................................. 17

Revision history ...................................................18

15

Legal information .................................................19

Data sheet status ............................................... 19

Definitions ...........................................................19

Disclaimers .........................................................19

Trademarks ........................................................ 20

15.1

15.2

15.3

15.4

© Nexperia B.V. 2017. All rights reserved

For more information, please visit: http://www.nexperia.com

For sales office addresses, please send an email to: salesaddresses@nexperia.com

Date of release: 04 February 2016

©

PBSS4260PANPS

All information provided in this document is subject to legal disclaimers.

Nexperia B.V. 2017. All rights reserved

Product data sheet

4 February 2016

21 / 21

NEXPERIA [ Nexperia ]

NEXPERIA [ Nexperia ]