µPD75216A

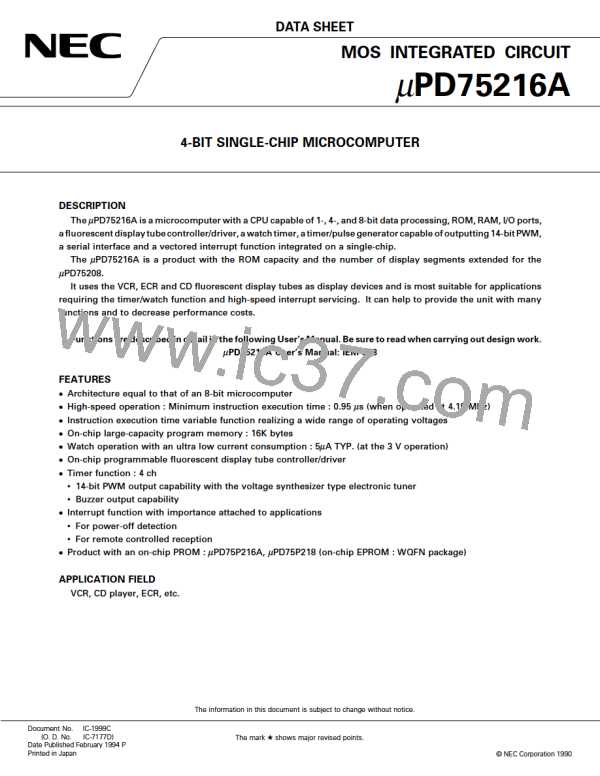

Table 8-1 Hardware Statuses after Reset

RESET Input upon

Power-on Reset or

in Operation

Hardware

RESET Input in Standby Mode

Program counter (PC)

PSW Carry flag (CY)

Sets the low-order 6 bits of program

memory address 0000H to PC13-8 and

the contents of address 0001H to PC7-0.

Same as left

Hold

Undefined

0

0

Skip flag (SK0 to SK2)

0

Interrupt status flag (IST0, IST1)

Bank enable flags (MBE, RBE)

0

Sets bit 6 of program memory address

0000H to RBE and bit 7 to MBE.

Same as left

Stack pointer (SP)

Undefined

Undefined

Data memory (RAM)

Hold*1

Undefined

General registers (X, A, H, L, D, E, B, C)

Bank select registers (MBS, RBS)

Basic interval Counter (BT)

Hold

Undefined

0, 0

0, 0

Undefined

Undefined

timer

Mode register (BTM)

0

0

Timer/event

counter

Counter (T0)

0

0

Modulo register (TMOD0)

Mode register (TM0)

FFH

FFH

0

0

Timer/pulse

generator

Modulo register (MODH, MODL)

Mode register (TPGM)

Hold

Undefined

0

0

Watch timer

Mode register (WM)

0

0

Serial

Shift register (SIO)

Hold

Undefined

interface

Mode register (SIOM)

Only bit 4 set to 1, other bits set to 0

Only bit 4 set to 1, other bits set to 0

Clock

generator

Processor clock control register (PCC)

System clock control register (SCC)

Interrupt request flag (IRQ×××)

Interrupt enable flag (IE×××)

Priority select register (IPS)

INT0 and INT1 mode registers (IM0, IM1)

Output buffer

0

0

0

Reset (0)

0

0

Interrupt

Reset (0)

0

0

0

0, 0

Off

0, 0

Digital port

Port H

Off

Output latch

Clear (0)

0

Clear (0)

Input/outputmoderegister(PMGA,PMGB)

Output latch

0

Hold

0

Undefined

FIP controller/ Display mode register (DSPM)

0

driver

Digit select register (DIGS)

1000B

0

1000B

Dimmer select register (DIMS)

Display data memory

0

Undefined

Off

Hold

Off

Output buffer

Power on flag (PONF)

Hold

1 or undefined*2

*

1. Data of data memory addresses 0F8H to 0FDH becomes indeterminate by RESET input.

2. 1 upon power-on reset, indeterminate after RESET input in operation.

33

NEC [ NEC ]

NEC [ NEC ]