CHAPTER 10 8-BIT A/D CONVERTER (µPD789426 AND 789446 SUBSERIES)

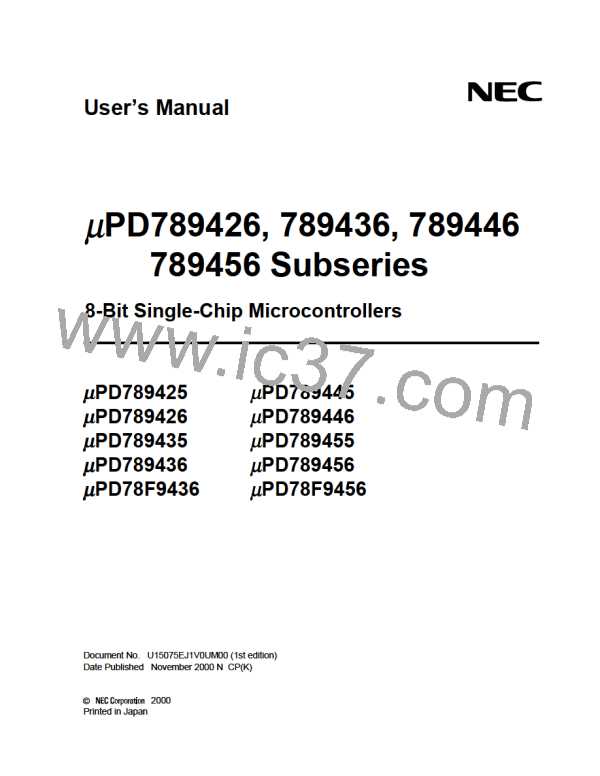

Figure 10-1. Block Diagram of 8-Bit A/D Converter

AVDD

P-ch

ANI0/P60

ANI1/P61

ANI2/P62

ANI3/P63

ANI4/P64

ANI5/P65

Sample & hold circuit

Voltage comparator

AVSS

AVSS

Successive

approximation

register (SAR)

INTAD0

Controller

A/D conversion result

register 0 (ADCR0)

3

ADS02 ADS01 ADS00

ADCS0 FR02 FR01 FR00

Analog input channel

specification register 0 (ADS0)

A/D converter mode

register 0 (ADM0)

Internal bus

(1) Successive approximation register (SAR)

The SAR receives the result of comparing an analog input voltage and a voltage at a voltage tap

(comparison voltage), received from the series resistor string, starting from the most significant bit (MSB).

Upon receiving all the bits, down to the least significant bit (LSB), that is, upon the completion of A/D

conversion, the SAR sends its contents to A/D conversion result register 0 (ADCR0).

(2) A/D conversion result register 0 (ADCR0)

ADCR0 holds the result of A/D conversion. Each time A/D conversion ends, the conversion result in the

successive approximation register is loaded into ADCR0, which is an 8-bit register.

ADCR0 can be read with an 8-bit memory manipulation instruction.

RESET input makes ADCR0 undefined.

(3) Sample & hold circuit

The sample & hold circuit samples consecutive analog inputs from the input circuit, one by one, and sends

them to the voltage comparator. The sampled analog input voltage is held during A/D conversion.

User’s Manual U15075EJ1V0UM00

184

NEC [ NEC ]

NEC [ NEC ]