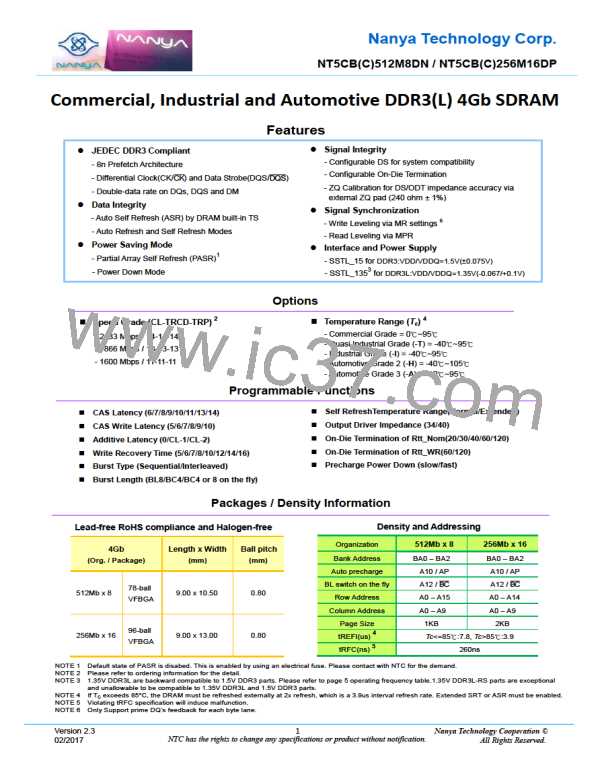

DDR3(L) 4Gb SDRAM

NT5CB(C)512M8DN / NT5CB(C)256M16DP

Dynamic ODT

In certain application cases and to further enhance signal integrity on the data bus, it is desirable that the termination

strength of the DDR3(L) SDRAM can be changed without issuing an MRS command. This requirement is supported by the

“Dynamic ODT” feature as described as follows:

Functional Description

The Dynamic ODT Mode is enabled if bit (A9) or (A10) of MR2 is set to ‘1’. The function is described as follows:

Two RTT values are available: RTT_Nom and RTT_WR.

The value for RTT_Nom is preselected via bits A[9,6,2] in MR1.

The value for RTT_WR is preselected via bits A[10,9] in MR2.

During operation without write commands, the termination is controlled as follows:

Nominal termination strength RTT_Nom is selected.

Termination on/off timing is controlled via ODT pin and latencies ODTLon and ODTLoff.

When a Write command (WR, WRA, WRS4, WRS8, WRAS4, WRAS8) is registered, and if Dynamic ODT is enabled, the

termination is controlled as follows:

A latency ODTLcnw after the write command, termination strength RTT_WR is selected.

A latency ODTLcwn8 (for BL8, fixed by MRS or selected OTF) or ODTLcwn4 (for BC4, fixed by MRS or selected OTF) after the

write command, termination strength RTT_Nom is selected.

Termination on/off timing is controlled via ODT pin and ODTLon, ODTLoff.

The following table shows latencies and timing parameters which are relevant for the on-die termination control in Dynamic

ODT mode.

The dynamic ODT feature is not supported at DLL-off mode. User must use MRS command to set RTT_WR, MR2[A10,A9

= [0,0], to disable Dynamic ODT externally.

When ODT is asserted, it must remain high until ODTH4 is satisfied. If a Write command is registered by the SDRAM with

ODT high, then ODT must remain high until ODTH4 (BL=4) or ODTH8 (BL=8) after the Write command. ODTH4 and

ODTH8 are measured from ODT registered high to ODT registered low or from the registration of Write command until ODT

is register low.

Version 2.3

02/2017

76

Nanya Technology Cooperation ©

All Rights Reserved.

NANYA [ Nanya Technology Corporation. ]

NANYA [ Nanya Technology Corporation. ]