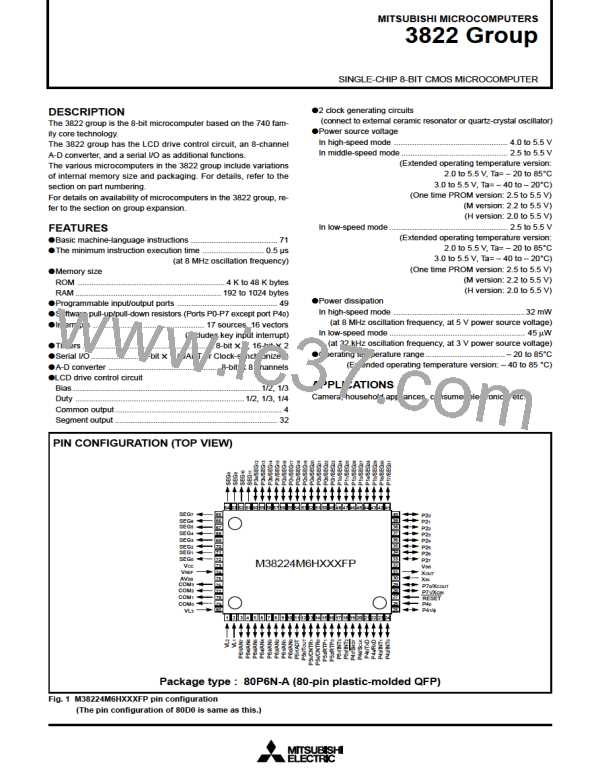

MITSUBISHI MICROCOMPUTERS

3822 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

Table 21 Timing requirements 1 (Standard, One Time PROM version)

(VCC = 4.0 to 5.5 V, VSS = 0 V, Ta = –20 to 85 °C, unless otherwise noted)

Limits

Unit

Symbol

Parameter

Min.

2

Typ.

Max.

tw(RESET)

tc(XIN)

Reset input “L” pulse width

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Main clock input cycle time (XIN input)

Main clock input “H” pulse width

Main clock input “L” pulse width

CNTR0, CNTR1 input cycle time

CNTR0, CNTR1 input “H” pulse width

CNTR0, CNTR1 input “L” pulse width

INT0 to INT3 input “H” pulse width

INT0 to INT3 input “L” pulse width

125

45

twH(XIN)

twL(XIN)

40

tc(CNTR)

twH(CNTR)

twL(CNTR)

twH(INT)

twL(INT)

tc(SCLK)

250

105

105

80

80

Serial I/O clock input cycle time (Note)

Serial I/O clock input “H” pulse width (Note)

Serial I/O clock input “L” pulse width (Note)

Serial I/O input set up time

800

370

370

220

100

twH(SCLK)

twL(SCLK)

t

su(RXD–SCLK)

th(SCLK–RXD) Serial I/O input hold time

Note: When bit 6 of address 001A16 is “1” (clock synchronous).

Divide this value by four when bit 6 of address 001A16 is “0” (UART).

Table 22 Timing requirements 2 (Standard, One Time PROM version)

(VCC = 2.5 to 4.0 V, VSS = 0 V, Ta = –20 to 85 °C, unless otherwise noted)

Limits

Symbol

Parameter

Unit

Min.

2

Typ.

Max.

tw(RESET)

tc(XIN)

Reset input “L” pulse width

µs

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Main clock input cycle time (XIN input)

Main clock input “H” pulse width

Main clock input “L” pulse width

CNTR0, CNTR1 input cycle time

CNTR0, CNTR1 input “H” pulse width

CNTR0, CNTR1 input “L” pulse width

INT0 to INT3 input “H” pulse width

INT0 to INT3 input “L” pulse width

125

45

twH(XIN)

twL(XIN)

40

tc(CNTR)

twH(CNTR)

twL(CNTR)

twH(INT)

twL(INT)

tc(SCLK)

500/(VCC-2)

250/(VCC-2)-20

250/(VCC-2)-20

230

230

2000

950

950

400

200

Serial I/O clock input cycle time (Note)

Serial I/O clock input “H” pulse width (Note)

Serial I/O clock input “L” pulse width (Note)

Serial I/O input set up time

twH(SCLK)

twL(SCLK)

t

su(RXD–SCLK)

th(SCLK–RXD) Serial I/O input hold time

Note: When bit 6 of address 001A16 is “1” (clock synchronous).

Divide this value by four when bit 6 of address 001A16 is “0” (UART).

52

MITSUBISHI [ Mitsubishi Group ]

MITSUBISHI [ Mitsubishi Group ]