MITSUBISHI MICROCOMPUTERS

3822 Group

SINGLE-CHIP 8-BIT CMOS MICROCOMPUTER

LCD Display RAM

LCD Drive Timing

Address 004016 to 004F16 is the designated RAM for the LCD dis-

play. When “1” are written to these addresses, the corresponding

segments of the LCD display panel are turned on.

The LCDCK timing frequency (LCD drive timing) is generated in-

ternally and the frame frequency can be determined with the

following equation;

(frequency of count source for LCDCK)

f(LCDCK) =

(divider division ratio for LCD)

f(LCDCK)

Frame frequency =

(duty ratio)

Bit

7

6

5

4

3

1

0

2

Address

SEG0

004016

004116

004216

004316

004416

004516

004616

004716

004816

004916

004A16

004B16

004C16

004D16

004E16

004F16

SEG1

SEG2

SEG3

SEG4

SEG5

SEG6

SEG7

SEG8

SEG9

SEG10

SEG12

SEG14

SEG16

SEG18

SEG20

SEG22

SEG24

SEG26

SEG28

SEG30

SEG11

SEG13

SEG15

SEG17

SEG19

SEG21

SEG23

SEG25

SEG27

SEG29

SEG31

COM0

COM3

COM2 COM1

COM2 COM1 COM0

COM3

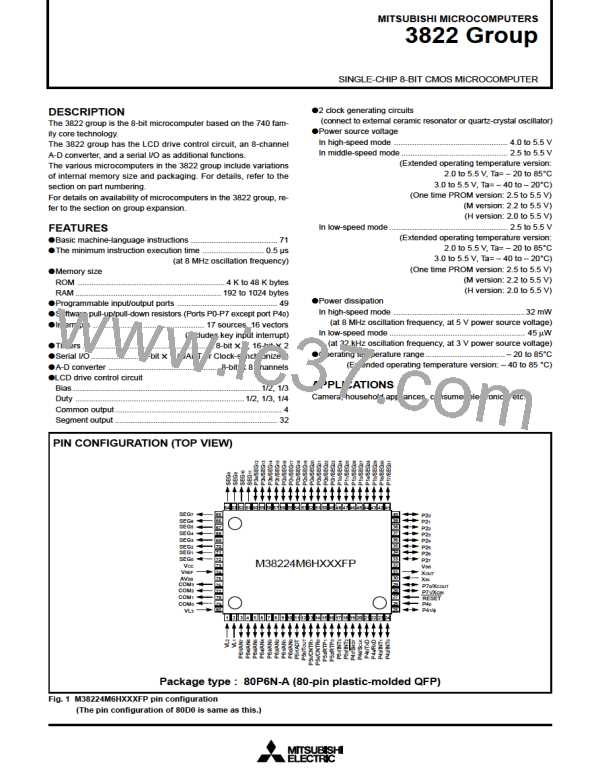

Fig. 35 LCD display RAM map

37

MITSUBISHI [ Mitsubishi Group ]

MITSUBISHI [ Mitsubishi Group ]