MT8806 ISO-CMOS

tCSS

tCSH

50%

50%

tRPW

CS

50%

50%

RESET

tSPW

STROBE

50%

50%

50%

tAS

ADDRESS

50%

50%

tAH

DATA

50%

tDS

50%

tDH

ON

SWITCH*

OFF

tR

tR

tS

tD

Figure 3 - Control Memory Timing Diagram

* See Appendix, Fig. A.7 for switching waveform

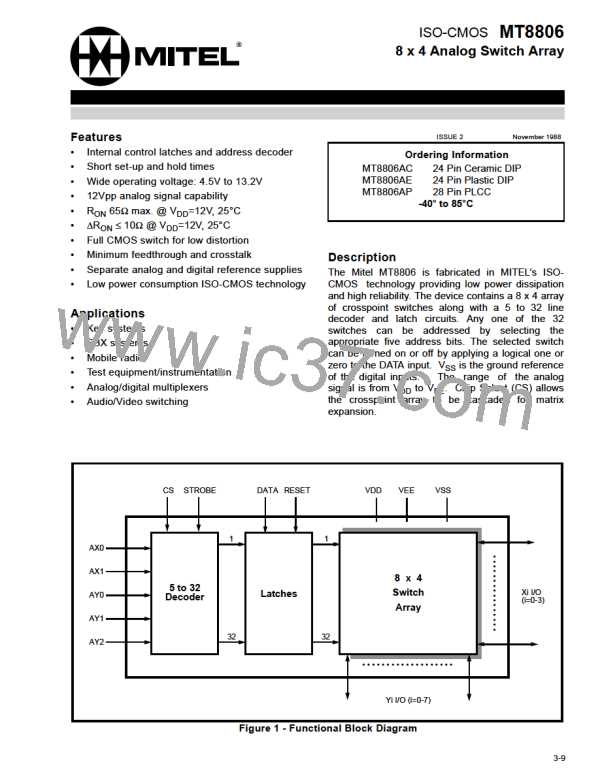

AX0

AX1

AY0

AY1

AY2

Connection

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

0

1

0

1

0

1

0

0

1

1

0

0

1

1

0

0

0

0

1

1

1

1

X0-Y0

X0-Y1

X0-Y2

X0-Y3

X0-Y4

X0-Y5

X0-Y6

X0-Y7

1

↓

0

↓

0

↓

0

↓

0

↓

X1-Y0

↓ ↓

1

0

1

1

1

X1-Y7

0

↓

1

↓

0

↓

0

↓

0

↓

X2-Y0

↓ ↓

0

1

1

1

1

X2-Y7

1

↓

1

↓

0

↓

0

↓

0

↓

X3-Y0

↓ ↓

1

1

1

1

1

X3-Y7

Table 1. Address Decode Truth Table

3-14

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]