MT8804A CMOS

50%

50%

MR

tAEW

50%

AE

50%

50%

tAS

ADDRESS

D0-D3

50%

50%

tAH

50%

tDS

50%

tDH

ON

SWITCH

OFF

tPLH/tPHL

tPAE

tMRR

tMR

tPLH/tPHL

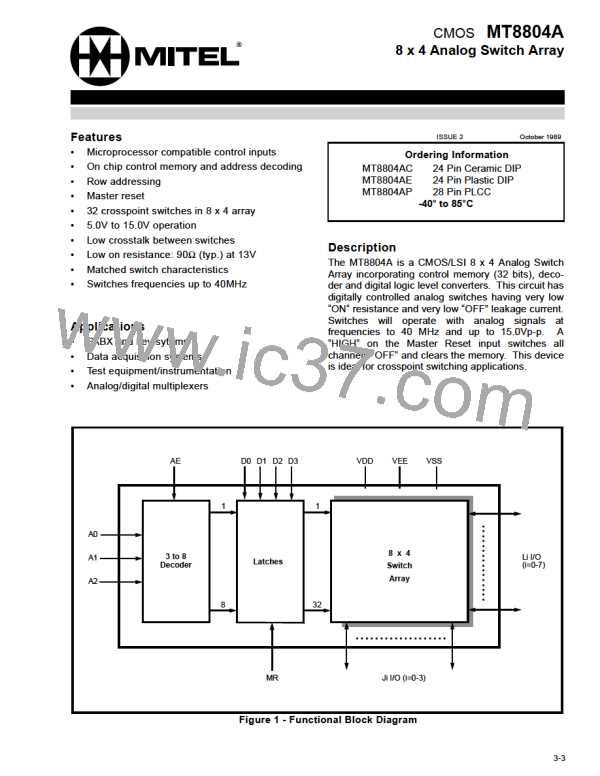

Figure 6 - Control Memory Timing Diagram

Input Data To Control

Junctors Connected To

Addressed Line

Memory

Address

Enable

AE

Address

Addressed

Line

Memory

Reset

MR

A2

X

A1

X

A0

X

D3

X

D2

D1

X

D0

X

J3

J2

J1

J0

1

0

X

0

ALL

X

X

All Switches "OFF"

No Change of State

X

X

X

NONE

X

X

X

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

L0

L0

L0

L0

L0

L0

L0

L0

L0

L0

L0

L0

L0

L0

L0

L0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

•

•

•

•

•

•

•

•

+

+

+

+

+

+

+

+

•

•

•

•

•

+

+

•

•

+

•

+

•

+

•

+

•

+

•

+

•

+

•

+

•

+

+

+

+

•

•

•

•

+

+

•

•

+

+

•

•

+

+

•

+

+

+

+

0

↓

1

↓

0

↓

0

↓

1

↓

L1

↓

0

↓

0

↓

0

↓

0

↓

•

↓

•

↓

•

↓

•

↓

0

1

0

0

1

L1

1

1

1

1

+

+

+

+

0

↓

1

↓

0

↓

1

↓

0

↓

L2

↓

0

↓

0

↓

0

↓

0

↓

•

↓

•

↓

•

↓

•

↓

0

1

0

1

0

L2

1

1

1

1

+

+

+

+

0

↓

1

↓

0

↓

1

↓

1

↓

L3

↓

0

↓

0

↓

0

↓

0

↓

•

↓

•

↓

•

↓

•

↓

0

1

0

1

1

L3

1

1

1

1

+

+

+

+

0

↓

1

↓

1

↓

0

↓

0

↓

L4

↓

0

↓

0

↓

0

↓

0

↓

•

↓

•

↓

•

↓

•

↓

0

1

1

0

0

L4

1

1

1

1

+

+

+

+

0

↓

1

↓

1

↓

0

↓

1

↓

L5

↓

0

↓

0

↓

0

↓

0

↓

•

↓

•

↓

•

↓

•

↓

0

1

1

0

1

L5

1

1

1

1

+

+

+

+

0

↓

1

↓

1

↓

1

↓

0

↓

L6

↓

0

↓

0

↓

0

↓

0

↓

•

↓

•

↓

•

↓

•

↓

0

1

1

1

0

L6

1

1

1

1

+

+

+

+

0

↓

1

↓

1

↓

1

↓

1

↓

L7

↓

0

↓

0

↓

0

↓

0

↓

•

↓

•

↓

•

↓

•

↓

0

1

1

1

1

L7

1

1

1

1

+

+

+

+

Table 1 - Address Decode Truth Table

NOTES:

0 - Low Logic Level

1 - High Logic Level

X - Don’t Care Condition

+ - Indicates Connection Between Junctor and Addressed Line

• - Indicates No Connection Between Junctor and Addressed Line

3-8

MITEL [ MITEL NETWORKS CORPORATION ]

MITEL [ MITEL NETWORKS CORPORATION ]