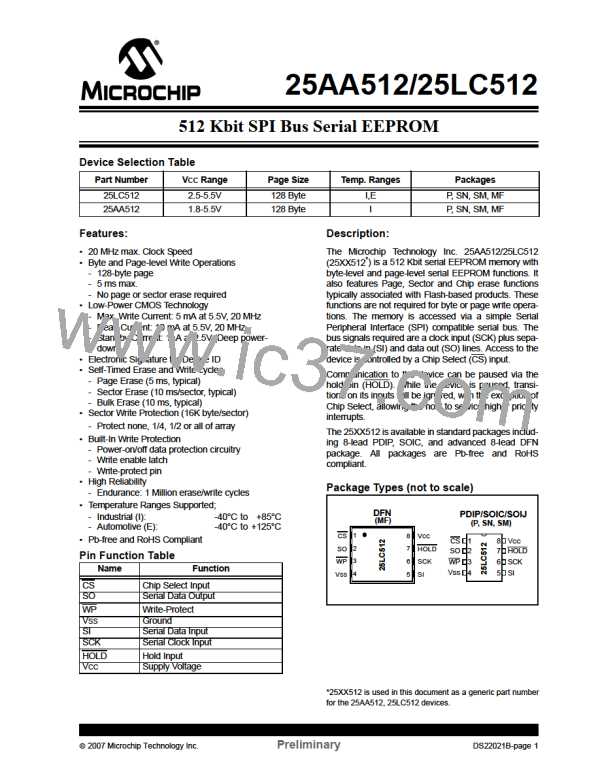

25AA512/25LC512

The Write-Protect Enable (WPEN) bit is a nonvolatile

bit that is available as an enable bit for the WP pin. The

Write-Protect (WP) pin and the Write-Protect Enable

(WPEN) bit in the STATUS register control the

programmable hardware write-protect feature. Hard-

ware write protection is enabled when WP pin is low

and the WPEN bit is high. Hardware write protection is

disabled when either the WP pin is high or the WPEN

bit is low. When the chip is hardware write-protected,

only writes to nonvolatile bits in the STATUS register

are disabled. See Table 2-4 for a matrix of functionality

on the WPEN bit.

2.5

Write Status Register Instruction

(WRSR)

The Write Status Register instruction (WRSR) allows the

user to write to the nonvolatile bits in the STATUS

register as shown in Table 2-2. The user is able to

select one of four levels of protection for the array by

writing to the appropriate bits in the STATUS register.

The array is divided up into four segments. The user

has the ability to write-protect none, one, two or all four

of the segments of the array. The partitioning is

controlled as shown in Table 2-3.

See Figure 2-7 for the WRSRtiming sequence.

TABLE 2-3:

ARRAY PROTECTION

Array Addresses

Write-Protected

Array Addresses

Unprotected

BP1

BP0

none

All (Sectors 0, 1, 2 & 3)

(0000h-FFFFh)

0

0

Upper 1/4 (Sector 3)

(C000h-FFFFh)

Lower 3/4 (Sectors 0, 1 & 2)

(0000h-BFFFh)

0

1

1

1

Upper 1/2 (Sectors 2 & 3)

(8000h-FFFFh)

Lower 1/2 (Sectors 0 & 1)

(0000h-7FFFh)

0

1

All (Sectors 0, 1, 2 & 3)

(0000h-FFFFh)

none

FIGURE 2-7:

WRITE STATUS REGISTER TIMING SEQUENCE (WRSR)

CS

0

1

2

3

4

5

6

7

8

9

10

11

12

13

14

1

15

0

SCK

SI

Instruction

Data to STATUS Register

7

6

5

4

3

2

0

0

0

0

0

0

0

1

High-Impedance

SO

DS22021B-page 12

Preliminary

© 2007 Microchip Technology Inc.

MICROCHIP [ MICROCHIP ]

MICROCHIP [ MICROCHIP ]