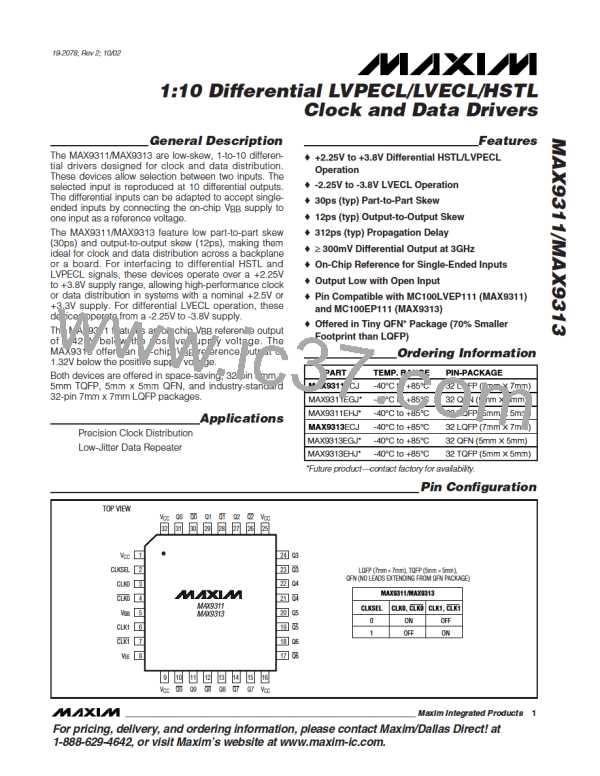

1:10 Differential LVPECL/LVECL/HSTL

Clock and Data Drivers

differential pair by matching the electrical length of the

traces.

Chip Information

TRANSISTOR COUNT: 250

Output Termination

Terminate outputs through 50Ω to V - 2V or use an

CC

equivalent Thevenin termination. When a single-ended

signal is taken from a differential output, terminate both

outputs. For example, if Q0 is used as a single-ended

output, terminate both Q0 and Q0.

CLK_

CLK_

V

IH

V

BB

V

IL

(CONNECTED TO CLK_)

V

Q_

Q_

OH

V

- V

OH OL

V

OL

Figure 1. Switching with Single-Ended Input

CLK_

CLK_

V

IHD

V

- V

IHD ILD

V

ILD

t

t

PLHD

PHLD

V

V

Q_

Q_

OH

OL

V

- V

OL

OH

80%

0 (DIFFERENTIAL)

80%

0 (DIFFERENTIAL)

20%

20%

(Q_) - (Q_)

t

t

F

R

Figure 2. Differential Transition Time and Propagation Delay Timing Diagram

8

_______________________________________________________________________________________

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]