±±15k EꢀDꢁ-rotected, ±µA, ±6Mbps, Dual/Quad

Lowꢁkoltage Level Translators in UCꢀ-

IEC 1000-4-2

The IEC 1000-4-2 standard covers ESD testing and

performance of finished equipment; it does not specifi-

cally refer to integrated circuits. The MAX3372E–

MAX3379E and MAX3390E–MAX3393E help to design

equipment that meets Level 3 of IEC 1000-4-2, without

the need for additional ESD-protection components.

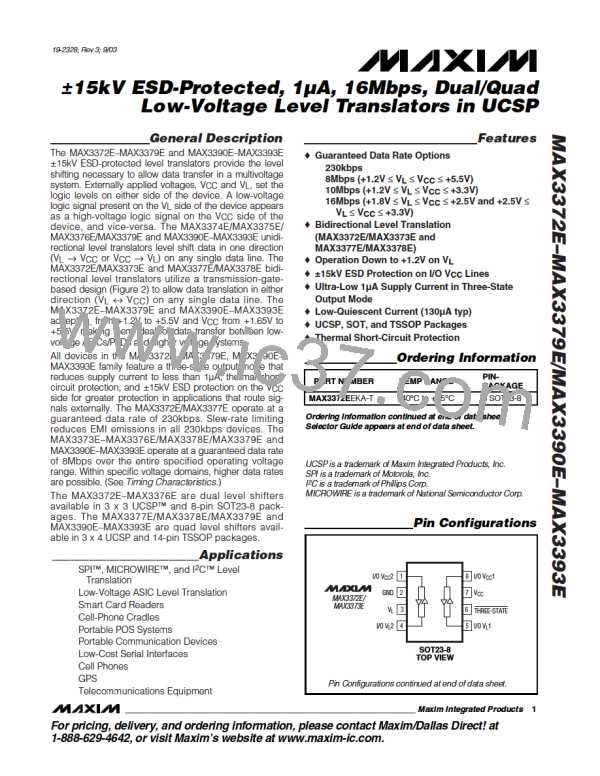

±±15k EꢀD -rotection

As with all Maxim devices, ESD-protection structures are

incorporated on all pins to protect against electrostatic

discharges encountered during handling and assembly.

The I/O V

lines have extra protection against static

CC

electricity. Maxim’s engineers have developed state-of-

the-art structures to protect these pins against ESD of

15kV without damage. The ESD structures withstand

high ESD in all states: normal operation, three-state out-

put mode, and powered down. After an ESD event,

Maxim’s E versions keep working without latchup,

whereas competing products can latch and must be

powered down to remove latchup.

The major difference between tests done using the

Human Body Model and IEC 1000-4-2 is higher peak cur-

rent in IEC 1000-4-2, because series resistance is lower

in the IEC 1000-4-2 model. Hence, the ESD withstand

voltage measured to IEC 1000-4-2 is generally lower than

that measured using the Human Body Model. Figure 4a

shows the IEC 1000-4-2 model, and Figure 4b shows the

current waveform for the 8kV, IEC 1000-4-2, Level 4,

ESD contact-discharge test.

ESD protection can be tested in various ways. The I/O

V

lines of this product family are characterized for

CC

protection to the following limits:

The air-gap test involves approaching the device with a

charged probe. The contact-discharge method connects

the probe to the device before the probe is energized.

1) 15kV using the Human Body Model

2) 8kV using the Contact Discharge method specified

in IEC 1000-4-2

3) 10kV using IEC 1000-4-2’s Air-Gap Discharge

Machine Model

The Machine Model for ESD tests all pins using a

200pF storage capacitor and zero discharge resis-

tance. Its objective is to emulate the stress caused by

contact that occurs with handling and assembly during

manufacturing. Of course, all pins require this protec-

tion during manufacturing, not just inputs and outputs.

Therefore, after PC board assembly, the Machine

Model is less relevant to I/O ports.

method

ESD Test Conditions

ESD performance depends on a variety of conditions.

Contact Maxim for a reliability report that documents

test setup, test methodology, and test results.

Human Body Model

Figure 3a shows the Human Body Model and Figure 3b

shows the current waveform it generates when dis-

charged into a low impedance. This model consists of

a 100pF capacitor charged to the ESD voltage of inter-

est, which is then discharged into the test device

through a 1.5kΩ resistor.

R

1MΩ

R 1500Ω

D

C

I 100%

P

90%

PEAK-TO-PEAK RINGING

(NOT DRAWN TO SCALE)

I

r

DISCHARGE

RESISTANCE

CHARGE-CURRENT-

LIMIT RESISTOR

AMPERES

HIGH-

VOLTAGE

DC

DEVICE

UNDER

TEST

C

s

100pF

STORAGE

CAPACITOR

36.8%

SOURCE

10%

0

TIME

0

t

RL

t

DL

CURRENT WAVEFORM

Figure 3a. Human Body ESD Test Model

Figure 3b. Human Body Current Waveform

______________________________________________________________________________________ 13

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]