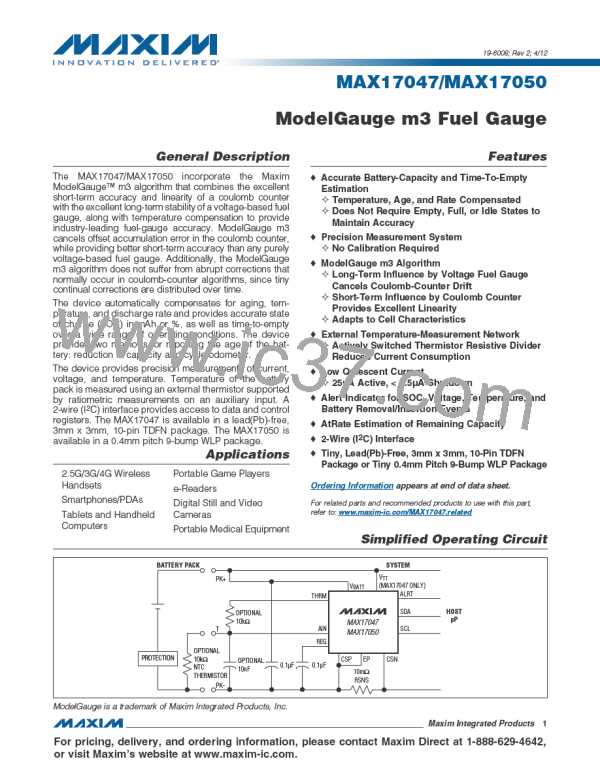

MAX17047/MAX17050

ModelGauge m3 Fuel Gauge

LS2:LS0—Learn Stage. See Figure 3 The Learn Stage

value controls the influence of the VFG on the mixing

algorithm. At power-up, Learn Stage defaults to 0h, mak-

ing the voltage fuel gauge dominate. Learn Stage then

advances to 7h over the course of two full cell cycles to

make the coulomb counter dominate. Host software can

write the Learn Stage value to 7h to advance to the final

stage at any time. Writing any value between 1h and

6h is ignored. Learn Stage reflects the D5, D6, and D7

bits of the Cycles register. Update the Cycles register

to advance to an intermediate state. For example, set

Cycles = 160% to advance to Learn Stage 5.

1 0 SOC Alerts are generated based on the SOC

MIX

register.

1 1 SOC Alerts are generated based on the SOC

VF

register.

MR4:MR0—Mixing Rate. This value sets the strength of

the servo mixing rate after the final mixing state has been

reached (> 2.08 complete cycles). The units are MR0 =

6.25FV, giving a range up to 19.375mA with a standard

0.010I sense resistor. Setting this value to 00000b dis-

ables servo mixing and the IC continues with time-con-

stant mixing indefinitely. The default setting is 18.75FV or

1.875mA with a standard sense resistor.

MiscCFG Register (2Bh)

The MiscCFG control register enables various other

functions of the device. The MiscCFG register default

values should not be changed unless specifically

required by the application. Figure 34 is the MiscCFG

register format:

enBi1—Enable reset on battery-insertion detection. Set

this bit to 1 to force a reset of the fuel gauge whenever a

battery insertion is detected based on AIN pin monitoring.

This bit is written to 1 at power-up.

FSTAT Register (3Dh)

The FSTAT register is a read-only register that monitors

the status of the ModelGauge algorithm. Do not write

to this register location. Figure 35 is the FSTAT register

format:

0—Bit must be written 0. Do not write 1.

1—Bit must be written 1. Do not write 0.

X—Don’t Care. Bit may read 0 or 1.

SACFG1:SACFG0—SOC Alert Config. SOC Alerts can

be generated by monitoring any of the SOC registers as

follows. SACFG defaults to 00 at power-up:

RelDt—Relaxed cell detection. This bit is set to a 1 when-

ever the ModelGauge m3 algorithm detects that the cell

is in a fully relaxed state. This bit is cleared to 0 whenever

a current greater than the Load threshold is detected.

See Figure 32.

0 0 SOC Alerts are generated based on the SOC

REP

register.

0 1 SOC Alerts are generated based on the SOC

AV

register.

MSB—ADDRESS 2Bh

LSB—ADDRESS 2Bh

SACFG SACFG

4

3

2

1

0

0

0

X

X

enBi1

0

MR

MR

MR

MR MR

1

0

0

1

0

MSb

LSb

MSb

0

LSb

MR UNITS: 6.25µV

Figure 34. MiscCFG Register Format (Input)

MSB—ADDRESS 3Dh

LSB—ADDRESS 3Dh

X

X

X

X

X

X

RelDt EDet

LSb

X

RelDt2

X

X

X

X

X

DNR

LSb

MSb

MSb

Figure 35. FSTAT Register Format (Output)

���������������������������������������������������������������� Maxim Integrated Products 26

MAXIM [ MAXIM INTEGRATED PRODUCTS ]

MAXIM [ MAXIM INTEGRATED PRODUCTS ]